- Ameya360 Component Supply Platform >

- Trade news >

- PA Semi, Apple ‘Interconnect’ at Startup

PA Semi, Apple ‘Interconnect’ at Startup

With a body of engineering experience at LSI, Cisco, SiByte, Broadcom, PA Semi and Apple, Shailendra Desai is confident of his knowledge in SoC designs and what needs to be done.

Desai was senior engineering manager at Apple from 2007 to January 2013, where he cut his teeth on issues of interconnect architecture, as well as third-party and in-house IP integration.

Desai said, “You can license individual IPs from various sources. But none of these IP vendors gave us a platform” to build and connect different IP blocks, in ways that might enable designers to optimize performance per watt for their SoCs.

Shailendra Desai

Desai established Provino Technologies Inc. in 2015 to create a scalable platform for SoCs and IP subsystems. Provino hopes to help designers of SoCs for consumer, automotive and industrial applications where safety, security and energy efficiency are paramount, he explained.

For consumer products like iPod, iPhone and iPad, for example, it all comes down to how fast and how many derivatives one can pump out based on a single platform, the Provino CEO observed. The same holds true in the IoT SoC market. While acknowledging that IoT is “not a very well-defined space yet,” Desai cited an even greater demand for designing configurable and scalable SoCs quickly — on one platform.

Early phase

Provino is still in its early phase. The company has neither talked to the press until now nor explained its technology in depth to industry analysts.

Provino nonetheless already has one unnamed Japanese automotive customer. Provino currently has 10 large customers evaluating its interconnect platform. “Not a single company has dropped thus far,” said Desai. Provino plans to go for series A funding in the first quarter of 2018.

The design challenges that Desai encountered with one client, while he was working as a consultant in 2013, foreshadowed similar problems across the board. His client designed an SoC that integrated various cores, including an FPGA. It was built by using Advanced eXtensible Interface (AXI). The company “couldn’t fit their design into an area they had. Meanwhile, AXI was creating a variety of problems such as congestions, latencies and performance,” Desai observed. “When I highlighted such issues in my report, the client said me, ‘Is that it? Can’t you solve the problem for us?’”

That client became Provino’s first customer. Provino today has 10 people working in California and 15 in India, and it’s hiring.

Interconnect: ‘Unsung hero’

During the interview, Desai confessed, “When I started Provino, I had no idea what others were doing” in the interconnect field.

As Mike Demler, a senior analyst at the Linley Group, put it, “Interconnect IP has been perhaps the unsung hero of the processor industry for at least 20 years. We just don’t hear about it as much as the latest CPU or GPU. ARM, Arteris, NetSpeed, and Sonics have a lot of expertise in this area.”

Demler explained, “Like any EDA tool and processor IP, there’s always room for improvement. I’d say that the application of machine learning, which NetSpeed is pioneering, could lead to big advances in SoC implementation.” After all, as he concluded, “Hooking up all the components of a billion-transistor chip is an incredibly complex task. Companies that can reduce design time and re-spin costs have an easy value proposition to win over customers.”

Desai told us that the multiple companies now pursuing the interconnect IP market gives him some comfort. “That means I am in the right market.” Indeed, Desai’s old colleagues at SiByte now hold positions at competing interconnect IP companies such as as Arteris and NetSpeed.

Building blocks of iFabric

So, what exactly is Provino’s interconnect platform?

Desai calls it “iFabric.” The list of iFabric’s building blocks is long, but it boils down to scalable architecture, a foundation for QoS (enabled by virtual channels), multi domain/topology support and integrated safety and security features.

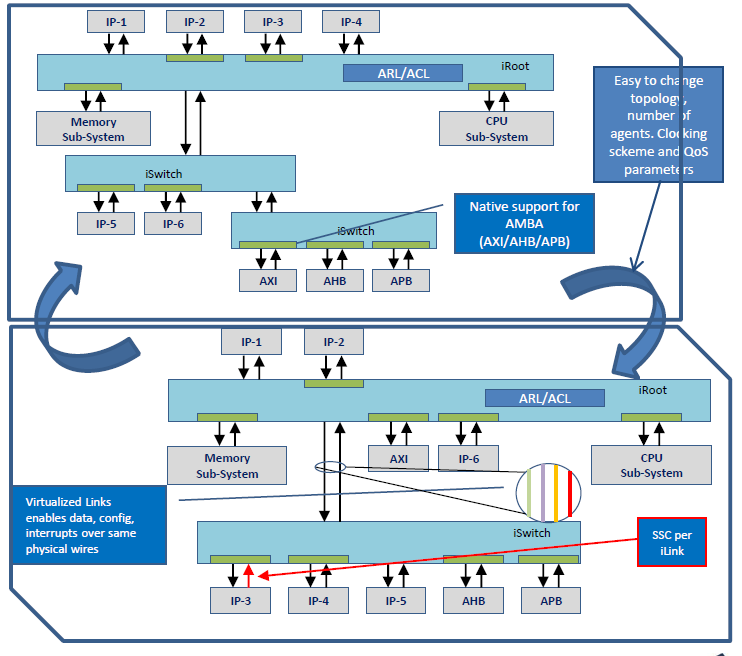

iFabric: Scalalbe and configurable architecture (Source: Provino)

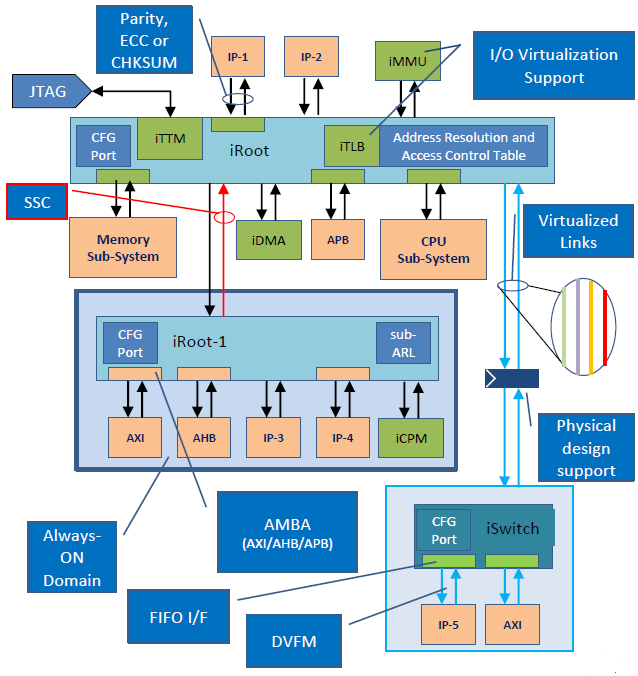

First and foremost, “iFabric is a packetized and serialized bus with a concept of virtual channel,” Desai explained. iFabric provides multiple clocking options from server-class (high-speed) to consumer devices. Support for popular IP interfaces (AXI 3/4, APB and AHB) eases the integration of third-party and in-house IPs, he explained. Stressing its scalable architecture, he noted, “You can add or remove IPs easily so that you can design derivative products quickly.”

Desai also pointed out that iFabric is built with a foundation for quality of service (QoS). In contrast to other solutions that tend to “suffer from head of line blocking and/or under-utilized resources,” iFabric provides “end-to-end non-blocking QoS,” he claimed. iFabric, designed to support “QoS, traffic shaping and monitoring,” comes with “dynamic arbitration scheme.”

An important element of iFabric is the concept of virtual channels. Provino noted that virtual channels are key to reducing wires. They provide non-blocking dynamic QoS and help effectively utilize key resources.

In addition, iFabric offers “physical design” support by providing “placement aware topology, protocol-based reset synchronization and parameterized timing slice insertion.” Speaking of power domain partitioning, Desai said that Provino’s approach enables “partitioning interconnect in optimal way based on topology and physical constraints.”

Provino’s iFabric offers both PCI and Device Order support, noted Desai. “The world today is in love with ARM. Its Device Order system is not only popular but it’s simpler to use.” In contrast, Intel’s PCIe is “a lot more complex, but when correctly implemented, it offers much higher performance,” he added. “I will not be surprised if PCIe trickles down to consumer systems. That’s why we made our system support both.”

Given the growing demand for safety and security in automotive and IoT devices, Desai believes iFabric’s integrated features will play an important role. Beyond supporting Trustzone, iFabric offers “tag and memory mapped access control.”

Inside the iFabric-based SoC, “our customers can use either their own protocols, or Provino’s own link-layer protocol,” according to Desai. Provino’s iLink protocol makes it easy to do pipe insertion between iFabric components, a feature that’s effective when adding features, he explained. Meanwhile, this iLink protocol also allows “centralized access control list for security features tag/ID-based routing,” Desai added, serving as a backbone for safety and security.

iFabric Interconnect Platform (Source: Provino)

Issues and opportunities

Asked to list issues to be solved by interconnect IP vendors, Richard Wawrzyniak, principal analyst for ASIC & SoC at Semico Research Corp., listed: security in the interconnect network, advanced power management techniques, cache coherency, providing hooks for other type of IP (debug IP, sensors), and extensions to the SoC architecture.

Wawrzyniak explained, “As device complexity has risen, and the need for complex interconnect IP to tie multiple IP blocks on the SoC together, the interconnect fabric is the ideal place to put robust security functions to ensure the fidelity of the data moving through the architecture.”

While Provino told EE Times that it provides security functions in its interconnect IP, Wawrzyniak wants more information on what they are. Provino needs to build up these features and make them as robust as possible, he noted.

During the interview, Provino also said iFabric allows for partitioning the interconnect IP to support multiple clock domains based on topology and physical constraints. Wawrzyniak said this is “a reasonable means of providing power management features, but is not necessarily cutting edge” when compared to what others are doing today.

Competitions

Take the example of Sonics, said Wawrzyniak.

“Sonics has offered advanced power management features as part of their interconnect IP in the form of Energy Processing Units (EPUs) and ICE-grain power architecture fabric, which allow SoC designers to control power consumption right down to the state machine level,” he explained. “In addition, Sonics has also partnered with Moortec to offer connections between Sonics' interconnect IP and Moortec's temperature sensors to enable temperature-compensated, dynamic voltage and frequency scaling (DVFS) in chip designs intended for power-sensitive devices such as mobile/handheld and the Internet of Things (IoT). This is a compelling strategy to allow SoC designers the maximum in flexibility to build in the right level of power management functionality for their silicon solutions.”

Speaking of other interconnectivity IP vendors who have pioneered the field and worked on cache coherency, the Semico Research analyst noted that Arteris, NetSpeed and Sonics all offer versions of their interconnect IP with features for cache coherency already built in.

As Wawrzyniak stressed, “One of the biggest benefits to interconnect IP is its ability to evolve and grow over time as the market requirements change. This is not automatic, but must be undertaken and directed by the designers – think one generation of silicon to the next. All the interconnect IP vendors have this as a main tenet of their approach to the market.”

Naturally, Provino emphasizes its mission to offer solid QoS features to the designer, using a platform approach. The startup also talks about making room for customization by its customers. But, this is an area that’s difficult to properly quantify, Wawrzyniak added, “since all the interconnect IP vendors would say the same thing.”

Varying needs for interconnect

In sum, interconnect issues for SoCs designs are broad and deep. The Linley Group’s Demler said, SoC designers’ challenges differ, “depending on the processor application as well as the particular subsystem within an SoC.”

Issues such as timing closure are universal, with no single set of requirements for interconnect use in modern processors, Demler explained. “Complex processors integrate a hierarchy of interconnects. That’s why you’ll find so many different interconnects in ARM’s CoreLink family.”

He said, “For a server processor, the primary issues might be cache coherence, bandwidth, and multicore capacity. For an automotive processor, you’ll have multiple interconnects within heterogeneous subsystems, and you need to address ISO 26262/ASIL requirements for redundancy. Mobile processors in battery-operated devices require cache coherence, I/O coherence, and integration with power management. An IoT processor also needs power management and security is a high priority.”

In short, “designers are challenged to integrate all of the subsystems in an SoC, so interconnect vendors must include tools to automate synthesis, timing closure, and verification.”

This explains why the industry might see more new IP suppliers braving the interconnect market.

Dan Dobberpuhl

As for Provino, Desai knows he has come to the market at the right time with the right technology. He explained that he posed his interconnect concept to Dan Dobberpuhl, founder of SiByte and PA Semi more than a few years ago. Citing a long working relationship with Dobberpuhl, Desai said, “We are lucky to get his encouragement, and have him as the chairman of Provino.” Others, said Desai, who have helped Provino include Amrjit Gill, founder of SiByte, PA Semi, Agnilux and Maginatics, and Mark Hayter, a renowned system/SoC architect and engineering director of Google’s Chrome Hardware.

Online messageinquiry

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| RB751G-40T2R | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| MC33074DR2G | onsemi | |

| CDZVT2R20B | ROHM Semiconductor |

| model | brand | To snap up |

|---|---|---|

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics | |

| BP3621 | ROHM Semiconductor |

- Week of ranking

- Month ranking

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: