功率MOS管总烧毁,看看是不是这些原因?

今天给大家讲一下关于MOS管烧毁的原因,MOS 管可能会遭受与其他功率器件相同的故障,例如过电压(半导体的雪崩击穿)、过电流(键合线或者衬底熔化)、过热(半导体材料由于高温而分解)。

更具体的故障包括栅极和管芯其余部分之前的极薄氧化物击穿,这可能发生在相对于漏极或者源极的任何过量栅极电压中,可能是在低至10V-15V 时发生,电路设计必须将其限制在安全水平。

还有可能是功率过载,超过绝对最大额定值和散热不足,都会导致MOS管发生故障。

接下来就来看看所有可能导致失效的原因。

过电压

MOS管对过压的耐受性非常小,即使超出额定电压仅几纳秒,也可能导致设备损坏。

MOS管的额定电压应保守地考虑预期的电压水平,并应特别注意抑制任何电压尖峰或振铃。

长时间电流过载

由于导通电阻相对较高,高平均电流会在MOS管中引起相当大的热耗散。

如果电流非常高且散热不良,则MOS管可能会因温升过高而损坏。

MOS管可以直接并联以共享高负载电流。

瞬态电流过载

持续时间短、大电流过载会导致MOS管器件逐渐损坏,但是在故障发生前MOS管的温度几乎没有明显升高,不太能察觉出来。(也可以看下面分析的直通和反向恢复部分)

击穿(交叉传导)

如果两个相对MOS管的控制信号重叠,则可能会出现两个MOS管同时导通的情况,这会使电源短路,也就是击穿条件。

如果发生这种情况,每次发生开关转换时,电源去耦电容都会通过两个器件快速放电,这会导致通过两个开关设备的电流脉冲非常短但非常强。

通过允许开关转换之间的死区时间(在此期间两个MOS管均不导通),可以最大限度地减少发生击穿的机会,这允许一个MOS管在另一个MOS管打开之前关闭。

没有续流电流路径

当通过任何电感负载(例如特斯拉线圈)切换电流时,电流关闭时会产生反电动势。在两个开关设备都没有承载负载电流时,必须为此电流提供续流路径。

该电流通常通过与每个开关器件反并联连接的续流二极管安全地引导回电源轨道。

当MOS管用作开关器件时,工程师可以简单获得MOS管固有体二极管形式的续流二极管,这解决了一个问题,但创造了一个全新的问题......

MOS管体二极管的缓慢反向恢复

诸如特斯拉线圈之类的高 Q 谐振电路能够在其电感和自电容中存储大量能量。

在某些调谐条件下,当一个MOS管关闭而另一个器件打开时,这会导致电流“续流”通过 MOS管的内部体二极管。

这个原本不是什么问题,但当对面的MOS管试图开启时,内部体二极管的缓慢关断(或反向恢复)就会出现问题。

与MOS管 自身的性能相比,MOS管 体二极管通常具有较长的反向恢复时间。如果一个 MOS管的体二极管在对立器件开启时导通,则类似于上述击穿情况发生“短路”。

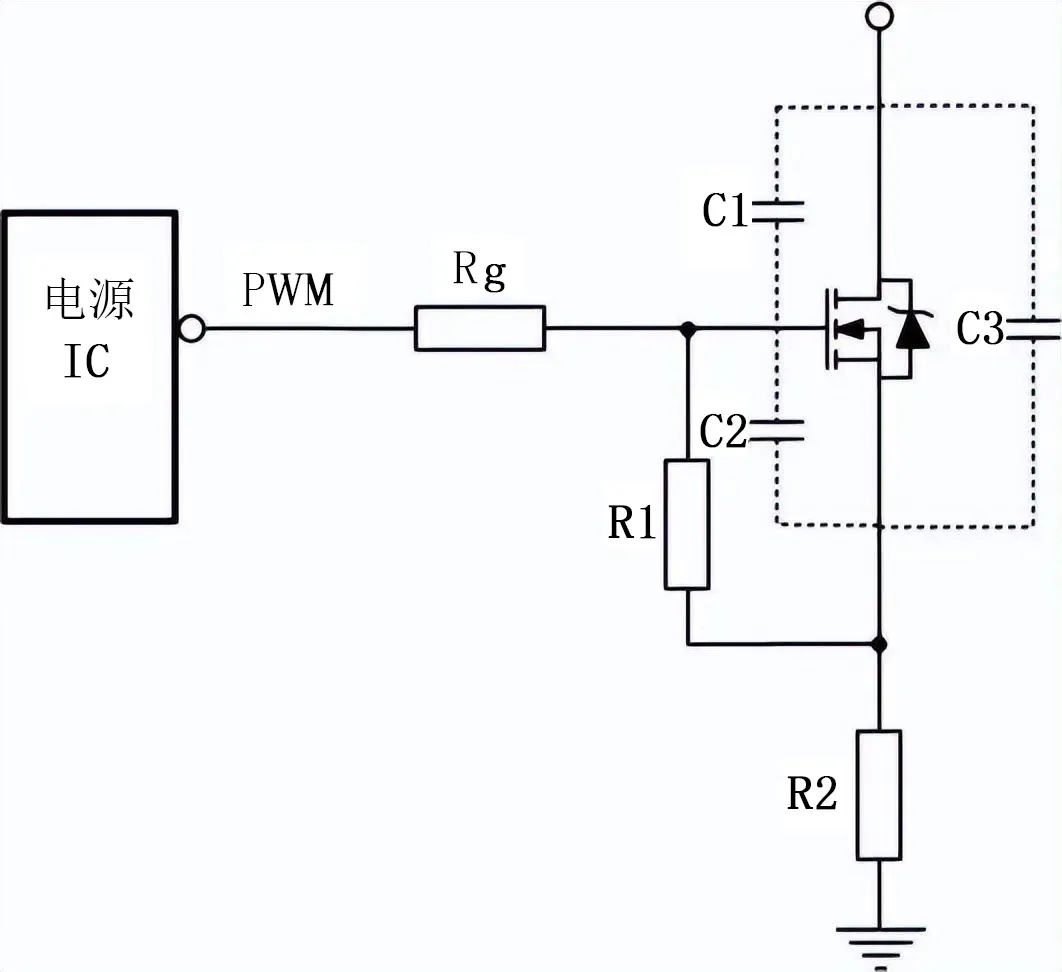

这个问题通常可以通过在每个MOS管周围添加两个二极管来缓解。

首先,肖特基二极管与MOS管源极串联,肖特基二极管可防止MOS管体二极管被续流电流正向偏置。其次,高速(快速恢复)二极管并联到MOS管/肖特基对,以便续流电流完全绕过MOS管和肖特基二极管。

这确保了MOS管体二极管永远不会被驱动导通,续流电流由快恢复二极管处理,快恢复二极管较少出现“击穿”问题。

过度的栅极驱动

如果用太高的电压驱动MOS管栅极,则栅极氧化物绝缘层可能会被击穿,从而导致MOS管无法使用。

超过 +/- 15 V的栅极-源极电压可能会损坏栅极绝缘并导致故障,应注意确保栅极驱动信号没有任何可能超过最大允许栅极电压的窄电压尖峰。

栅极驱动不足(不完全开启)

MOS管只能切换大量功率,因为它们被设计为在开启时消耗最少的功率。工程师应该确保MOS管硬开启,以最大限度地减少传导期间的耗散。

如果MOS管未完全开启,则设备在传导过程中将具有高电阻,并且会以热量的形式消耗大量功率,10到15伏之间的栅极电压可确保大多数MOS管完全开启。

缓慢的开关转换

在稳定的开启和关闭状态期间耗散的能量很少,但在过渡期间耗散了大量的能量。因此,应该尽可能快地在状态之间切换以最小化切换期间的功耗。由于MOS管栅极呈现电容性,因此需要相当大的电流脉冲才能在几十纳秒内对栅极进行充电和放电,峰值栅极电流可以高达一个安培。

杂散振荡

MOS管 能够在极短的时间内切换大量电流,输入也具有相对较高的阻抗,这会导致稳定性问题。在某些条件下,由于周围电路中的杂散电感和电容,高压MOS管会以非常高的频率振荡。(频率通常在低 MHz),但这样是非常不受欢迎的,因为它是由于线性操作而发生的,并且代表了高耗散条件。

这种情况可以通过最小化MOS管周围的杂散电感和电容来防止杂散振荡,还应使用低阻抗栅极驱动电路来防止杂散信号耦合到器件的栅极。

“米勒”效应

MOS管在其栅极和漏极端子之间具有相当大的“米勒电容”。在低压或慢速开关应用中,这种栅漏电容很少引起关注,但是当高压快速开关时,它可能会引起问题。

当底部器件的漏极电压由于顶部MOS管的导通而迅速上升时,就会出现潜在问题。

这种高电压上升率通过米勒电容电容耦合到MOS管的栅极,会导致底部MOS管的栅极电压上升,从而导致MOS管也开启,就会存在击穿情况,即使不是立即发生,也可以肯定MOS管故障。

米勒效应可以通过使用低阻抗栅极驱动器来最小化,该驱动器在关闭状态时将栅极电压钳位到 0 伏,这减少了从漏极耦合的任何尖峰的影响。在关断状态下向栅极施加负电压可以获得进一步的保护。例如,向栅极施加 -10 V电压将需要超过12V的噪声,以冒开启本应关闭的MOS管的风险。

对控制器的辐射干扰

想象一下,将 1pF 的电容从你的火花特斯拉线圈的顶部连接到固态控制器中的每个敏感点的效果,存在的数百千伏射频可以毫无问题地驱动大量电流通过微型电容器直接进入控制电路。

如果控制器没有放置在屏蔽外壳中,这就是实际会发生的情况。

控制电路的高阻抗点几乎不需要杂散电容即可导致异常操作,但运行不正常的控制器可能会尝试同时打开两个相反的MOS管 ,控制电子设备的有效射频屏蔽至关重要。

分离电源和控制电路也是非常理想的,电源开关电路中存在的快速变化的电流和电压仍然具有辐射显着干扰的能力。

对控制器的传导干扰

大电流的快速切换会导致电源轨上的电压骤降和瞬态尖峰。如果电源和控制电子设备共用一个或多个电源轨,则可能会对控制电路产生干扰。

良好的去耦和中性点接地是应该用来减少传导干扰影响的技术。作用于驱动MOS管的变压器耦合在防止电噪声传导回控制器方面非常有效。

静电损坏

安装MOS管或IGBT器件时,应采取防静电处理措施,以防止栅氧化层损坏。

高驻波比

这里要着重说一下,来自一位专业射频工程师的解释。

在脉冲系统中,VSWR不像在CW系统中那么大,但仍然是一个问题。

在CW系统中,典型的发射器设计用于50欧姆的电阻输出阻抗。工程师通过某种传输线连接到负载,希望负载和线路也是50欧姆,并且电力沿电线很好地流动。

但如果负载阻抗不是50欧姆,那么一定量的功率会从阻抗不连续处反射回来。但反射功率会导致几个潜在问题:

1、发射器看起来像一个负载并吸收了所有的功率,这不是一个好的现象。

例如,你的放大器效率为80%,你输入的功率1KW,通常情况下,设备的功耗为200W,最终的功耗为800W,如果所有800W的功耗都被反射回来,忽然之间,这些设备就需要消耗全部的功耗。

2、前向波和反射波的组合会在传输线中产生驻波,在相距1/2波长的点处会变得非常高,从而导致击穿或者其他不良情况,这本质上是表现负载阻抗不是预期的结果。

如果你有一个射频电源在几十兆赫兹,你可以装配一个开放的平行线传输线,在脉冲系统中,你可能会遇到沿线路传播的脉脉冲、阻抗不连续性、反射回以及与发送的下一个脉冲相加的问题。

反射脉冲是相同极性还是不同极性取决于距离和相对阻抗。

如果你有几个不匹配,可能会得到很多来回移动的脉冲,这些脉冲会加强或者取消。这个对于商业配电来说是一个真正的大问题,因为沿线路的传播时间是线路频率周期的很大一部分,当断路器打开和关闭以及雷击时会引起问题。

以上就是关于MOS管烧毁的原因分析。

上一篇:微波元器件有哪些

在线留言询价

如何区分MOS管的三个极

一文了解MOS管

一文了解常见的几种MOS管驱动电路

- 一周热料

- 紧缺物料秒杀

| 型号 | 品牌 | 询价 |

|---|---|---|

| BD71847AMWV-E2 | ROHM Semiconductor | |

| MC33074DR2G | onsemi | |

| RB751G-40T2R | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments | |

| CDZVT2R20B | ROHM Semiconductor |

| 型号 | 品牌 | 抢购 |

|---|---|---|

| ESR03EZPJ151 | ROHM Semiconductor | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics | |

| BP3621 | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments |

AMEYA360公众号二维码

识别二维码,即可关注

请输入下方图片中的验证码: