- Ameya360 Component Supply Platform >

- Trade news >

- Renesas Adds Capacitive Touch to Ultra-Low-Power RA0 MCUs

Renesas Adds Capacitive Touch to Ultra-Low-Power RA0 MCUs

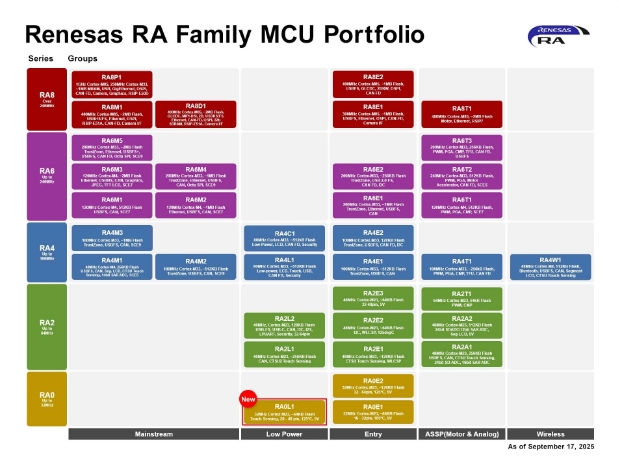

Renesas Electronics Corporation (TSE:6723), a premier supplier of advanced semiconductor solutions, today introduced the RA0L1 microcontroller (MCU) Group based on the Arm® Cortex®-M23 processor. The new devices offer extremely low power consumption and the industry’s best solution for quickly and economically implementing capacitive touch in battery-powered and other consumer electronics, appliances, white goods and industrial system controls.

Renesas introduced the RA0 MCU series in 2024 and it has quickly become very popular with a wide range of customers due to its affordability and low power consumption. With the addition of capacitive touch functionality, RA0L1 devices offer designers the ability to create responsive, attractive, low-power user interfaces at very low cost.

RA0L1 MCUs deliver industry-leading power consumption of only 2.9mA current in active mode, and 0.92mA in sleep mode. In addition, an integrated High-speed On-Chip Oscillator (HOCO) enables the fastest wake-up time for this class of microcontroller. The fast wake-up enables the RA0L1 MCUs to stay in Software Standby mode more of the time, where power consumption drops to a minuscule 0.25 µA. With this feature, current consumption can be reduced by up to 90 percent compared with other solutions.

Feature Set Optimized for Low Cost

The RA0L1 devices have a feature set optimized for cost-sensitive applications. They offer a wide operating voltage range of 1.6V to 5.5V so customers don’t need a level shifter/regulator in 5V systems. The RA0L1 MCUs also integrate multiple communications interfaces, analog functions, safety functions and security functionality to reduce customer BOM cost. A wide range of packaging options is also available, including a tiny 4mm x 4mm 24-pin QFN.

In addition, the new MCU’s high-precision (±1.0%) HOCO improves baud rate accuracy and enables designers to forego a standalone oscillator. Unlike other HOCOs in the industry, it maintains this precision in environments from -40°C to 125°C. This wide temperature range enables customers to simplify thermal design by avoiding costly and time-consuming “trimming,” even after the reflow process.

Renesas Capacitive Touch Leadership

Renesas provides industry-leading capacitive touch technology, ensuring customers can quickly and cost-effectively implement high-quality touch interfaces in a variety of systems. Its self-capacitance method simplifies waterproof design, offering simpler design and reduced complexity compared to mutual capacitance solutions. Renesas’ multi-frequency measurement meets IEC61000 4-3 Level 4 standards, making it ideal for medical applications that demand robust protection from electromagnetic interference. Renesas also offers specialized development resources for capacitive touch, including the QE for Capacitive Touch that streamlines sensitivity adjustments for capacitive touch buttons, speeding up development.

“The RA0L1 combines the industry-leading power consumption and cost-effectiveness of our RA0 Series MCUs with our unmatched capacitive touch technology and tools,” said Daryl Khoo, Vice President of the Embedded Processing Marketing Division at Renesas. “We look forward to the many innovative touch interface solutions that our customers will create using these devices.”

Key Features of the RA0L1 Group MCUs

Core: 32MHz Arm Cortex-M23

Memory: Up to 64KB integrated Code Flash memory and 16KB SRAM

Extended Temperature Range: Ta -40°C to 125°C

Timers: Timer array unit (16b x 8 channels), 32-bit interval timer (8b x 4 channels), RTC

Communications Peripherals: 3 UARTs, 2 Async UART, 6 Simplified SPIs, 2 I2C, 6 Simplified I2Cs

Analog Peripherals: 12-bit ADC, temperature sensor, internal reference voltage

HMI: Capacitive Touch (up to 24 channels), Controlled Current Drive Port (up to 8)

Safety: SRAM parity check, invalid memory access detection, frequency detection, A/D test, output level detection, CRC calculator, register write protection

Security: Unique ID, TRNG, Flash access window, Flash read protection

Packages: 24-, 32- and 48-pin QFNs, 32-, 48-pin LQFP, 20-pin LSSOP

The new RA0L1 Group MCUs are supported by Renesas’ Flexible Software Package (FSP). The FSP enables faster application development by providing all the infrastructure software needed, including multiple RTOS, BSP, peripheral drivers, middleware, connectivity, networking, and security stacks as well as reference software to build complex AI, motor control and cloud solutions. It allows customers to integrate their own legacy code and choice of RTOS with FSP, thus providing full flexibility in application development. Using the FSP will ease migration to and from other RA family devices.

Winning Combinations

Renesas has combined the new RA0L1 Group MCUs with numerous compatible devices from its portfolio to offer a wide array of Winning Combinations, including the Capacitive Touch Remote Controller. Winning Combinations are technically vetted system architectures from mutually compatible devices that work together seamlessly to bring an optimized, low-risk design for faster time to market. Renesas offers more than 400 Winning Combinations with a wide range of products from the Renesas portfolio to enable customers to speed up the design process and bring their products to market more quickly.

Availability

The RA0L1 Group MCUs are available now, along with the FSP software, the RA0L1 Fast Prototyping Board and the RA0L1 Renesas Solution Starter Kit for Cap Touch. Samples and kits can be ordered either on the Renesas website or through AMEYA360.

Online messageinquiry

Renesas Develops SoC Technologies for Automotive Multi-Domain ECUs Essential for the SDV Era

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| BD71847AMWV-E2 | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments | |

| MC33074DR2G | onsemi | |

| CDZVT2R20B | ROHM Semiconductor | |

| RB751G-40T2R | ROHM Semiconductor |

| model | brand | To snap up |

|---|---|---|

| BP3621 | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics |

- Week of ranking

- Month ranking

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: