- Ameya360 Component Supply Platform >

- Trade news >

- 全球晶圆大厂:先进制程的较量出现分化

全球晶圆大厂:先进制程的较量出现分化

摩尔定律正在逐渐放缓,想要遵循摩尔定律就需要投入越来越高的成本,这也使得愿意向12nm以下前进的客户越来越少。

从目前来看,采用12nm节点以下技术的主要客户还集中在智能手机等少数领域,各大晶圆厂在先进制程上的布局都有所变化。集微网将介绍2018年以来各大晶圆厂先进制程的进展,以及对于未来的展望。

台积电:7nm占比稳步提升,5nm将试产

在7nm技术路线的选择上,全球最大芯片代工企业台积电务实地在第一代放弃EUV(极紫外光刻),同时上马整合扇出封装技术提升可靠度,最终使得自己的进度超越三星,从而赢下包括华为、AMD、苹果等一众关键客户。

2018年4月,台积电表示,该公司将开始生产7nm处理器。6月,根据供应链消息,台积电着手将其7nm制程工艺扩大到大规模生产,从而能够满足客户对其需求。

台积电第三季度财报显示,7nm制程营收已占晶圆销售金额的11%。在7nm制程营收上扬的同时,台积电的第二代7nm工艺(CLNFF+/N7+)也在下半年成功流片,相较于第一代7nm DUV,第二代7nm EUV能将晶体管密度提升20%,同等频率下功耗可降低6-12%。

台积电总裁魏哲家表示,采用EUV 设备的第二代7nm产品进度依预期会在2019年量产,客户大量采用预估则落在2020 年。

另外,在台积电积极发展的第2代采用EUV技术的7nm制程开始进行投片同时,最新一代全程采用EUV 技术的5 nm制程将于2019 年的四月进行风险试产。

三星:7nm姗姗来迟,5nm提上日程

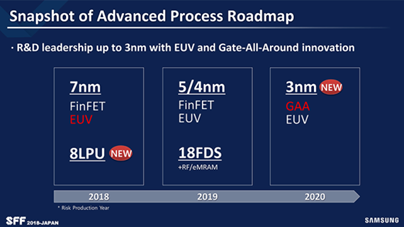

2018年10月,三星宣布7nm LPP(Low Power Plus)制程已进入量产阶段,并在工艺中成功应用极紫外光(EUV)微影技术。

三星电子的7nm LPP工艺相比上一代10nm FinFET的面积减少了40%,性能提升20%,耗电减少50%,消耗的掩膜也减少了20%。

目前,高通新一代的5G基带会采用三星的7nm LPP工艺。12月, IBM也宣布 POWER处理器和LinuxONE系统的处理器等,未来都将采用三星的7nm LPP工艺。

另一方面,2019年,三星计划将风险性试产的5nm和4nm,同样也会采用EUV技术。而首度导入闸极全环(GAA)晶体管的3nm工艺预计将在2020年风险试产。

英特尔: 14nm产能不够,10nm继续推迟

英特尔自2014年进入14nm制程时代,先进制程推进便原地踏步,原预定2016年中登场的10nm放量时程一再延迟。

一方面,进入2018年,英特尔在处理器路线图上遭遇了难题,核心问题在于10nm工艺难产,10nm Cannon Lake处理器预计于2019年第4季才会上市,英特尔不得不继续使用14nm工艺再撑一年。

尽管英特尔曾表示自己的10nm在工艺上远超友商台积电和三星的7nm,但实际拿出的基于Cannon Lake的 Core i3-8121U连核显都没有,同频性能和能耗比甚至不如目前的14nm。

另一方面,2018年9月,宏碁在内的多家客户共同表示,英特尔14nm的产品供货不足,据报道,其产能缺口一度接近50%。英特尔甚至还将一部分基础芯片交由台积电代工,同时产能扩增也在匆忙进行。

除了2019年将面世的10nm,英特尔还暗示7nm产品可能比预期的更早,即在10nm制程的4年后上市。

英特尔指出,7nm开发是由一个独立的团队的独立作业,更表示该团队已经从10nm经验中汲取了大量经验,并制造出更高的晶体管密度,功率和性能以及进度可预测性,10nm处理器的递延并没有阻碍其7nm处理器的发展。

联电:赚钱第一!停止12nm以下先进制程研发

2018年8月,台积电正在琢磨第二代7nm工艺,而同为台湾晶圆代工厂的联电在这时却宣布将停止12nm以下先进工艺的研发,在晶圆代工市场上不再拼技术,更看重投资回报率,赚钱第一。

2017年联电的14nm成功量产,短短一年后就决定不再投资12nm以下的先进制程,究竟是为什么呢?

据分析,过去的联电由于过度的投资先进制程,导致每次生产时产能利用率必须达到9成以上,才能盈利,而这样的营收方式显然不能长久,于是联电转变布局,选择把“钱用在正确的地方”。

不过,根据联电所述,他们未来还会投资研发14nm及改良版的12nm工艺,不过更先进的7nm及未来的5nm等工艺不会再大规模投资了。

格芯:差异化才是出路,7nm不搞了

2018年年初,格芯放话将于年底开始量产7纳米芯片,首位客户为AMD。同时还表示准备在生产线内引进用于先进制程的EUV设备。

然而8月29日,格芯突然宣布将搁置7nm FinFET项目,并调整相应研发团队来支持强化的产品组合方案,转攻ASIC市场,建立了独立于晶圆代工业务外的ASIC业务全资子公司。

格芯表示,微缩的速度正在逐渐放缓,先进节点的吸引力正在减小,格芯将会相应地优化开发资源,让14/12nm FinFET制程能够被更多的客户所使用,同时还提供包括射频、嵌入式存储器和低功耗等一系列创新IP及功能,更好的实现差异化。

中芯国际:28nm HKC持续上量,14nm呼之欲出

中芯国际的28nm在2017 年的收入占比中超预期达标,梁梦松博士出任联合CEO后,带来了雄厚的技术水平和先进的管理模式,加强了研发队伍的建设,调整更新了14nm FinFET规划,将3D FinFET 工艺锁定在高性能运算、低功耗芯片应用上。

2018年3月,中芯国际预计, 14 nm将比原计划提前半年投产。5月份,中芯国际向ASML订购新型EUV光刻机,这台机器价值1.2亿美元,预期将于2019年年初交付。另外,中芯国际预计其14nm工艺也将在2019年上半年量产,不知这台EUV届时是否会投入14nm的生产当中。

8月9日,中芯国际在第二季的财报会议上表示,14nm FinFET技术开发上获得重大进展,第一代FinFET技术研发已进入客户导入阶段。28nm HKC持续上量,同时28nm HKC+技术的开发工作也已完成。

华力微电子:28nm进入量产,14nm只是时间问题

中芯国际之外,华虹集团旗下的上海华力半导体也是国内重要的晶圆代工厂。2018年10月18日,华力二期工程正式投产,该项目总投资387亿元,12英寸月产能可达4万片晶圆,工艺等级涵盖28到14nm。

根据《解放日报》的消息,该项目建成后,华虹集团的集成电路制造能力将覆盖0.5微米到14纳米各工艺技术平台,制造规模进入全球前五位,工艺技术进入全球第一梯队。

12月11日,上海华力与联发科技共同宣布,在两家公司的互相信任及持续努力下,基于上海华力28nm低功耗工艺平台的一颗无线通讯数据处理芯片成功进入量产阶段。

华虹集团董事长张素心表示,公司目前28nm工艺产品良率达到93-98%,2020年将具备14nm FinFET产品生产能力。

随着摩尔定律的放缓,制程的缩小越来越困难,只有像台积电和三星这样的老牌劲旅才有实力跟精力去继续拓展。虽然市面上目前最新的只有7nm的制程,但是5nm、3nm量产已经被提上了日程,更有科学家已经实现了1nm级别的工艺,究竟半导体工艺的极限在哪里,而摩尔定律是否会被终结,这些只有留给时间去证明了!

Previous:被动原器件需求大增,富满电子拟在天津开展 MLCC 研发制造

Next:晋华DRAM团队回流台湾,转往华邦电等厂

Online messageinquiry

一文学习晶圆厂各环节术语中英文释义

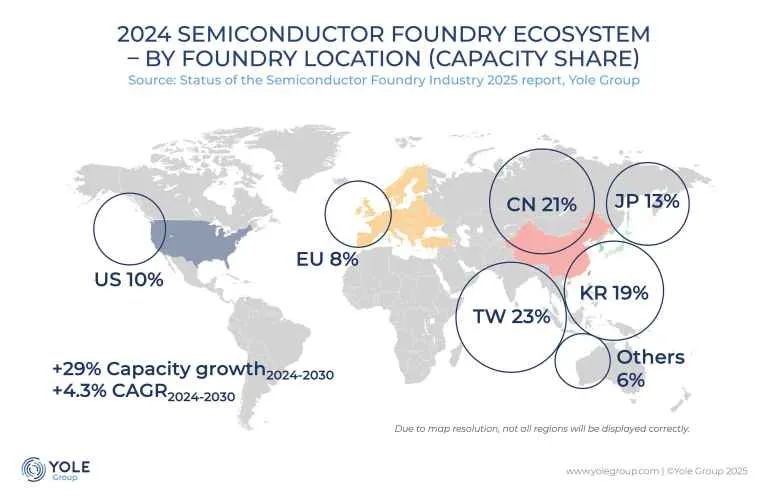

中国大陆将成全球最大晶圆代工中心!

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| BD71847AMWV-E2 | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments | |

| MC33074DR2G | onsemi | |

| RB751G-40T2R | ROHM Semiconductor | |

| CDZVT2R20B | ROHM Semiconductor |

| model | brand | To snap up |

|---|---|---|

| ESR03EZPJ151 | ROHM Semiconductor | |

| BP3621 | ROHM Semiconductor | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics | |

| TPS63050YFFR | Texas Instruments | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: