mos管和运算放大器的区别 场效应管和mos管的区别

综mos管和运算放大器是电子领域中常见的两种器件。mos管是一种场效应管类型,被广泛应用于数字和模拟电路中,具有高输入阻抗和低输出阻抗。而运算放大器是一种有源器件,用于信号放大和运算电路中,具有非常高的开环增益和多种功能。场效应管是一个更大的概念,包含了多种类型的管子,如JFET和IGBT等。mos管是场效应管的一种,以金属-氧化物-半导体结构为基础,具有更好的控制性能和应用灵活性。

一、mos管和运算放大器的区别

mos管(Metal-Oxide-Semiconductor Field-Effect Transistor)和运算放大器(Operational Amplifier)是电子领域中常见的两种器件。尽管它们在电路中扮演不同的角色,但有时可能会引起混淆。下面将详细介绍mos管和运算放大器之间的区别。

1、 mos管

mos管是一种半导体器件,也被称为场效应管(Field-Effect Transistor,FET)。它由源极、漏极和栅极组成,并通过在栅极上加上适当的电压来控制漏极与源极之间的电流。mos管存在两种主要类型:MOSFET(金属-氧化物-半导体场效应晶体管)和CMOS(互补金属-氧化物-半导体)。

mos管广泛应用于数字和模拟电路中。它们具有高输入阻抗、低输出阻抗和快速开关特性,可实现强大的放大、开关和驱动功能。mos管的工作原理基于对沟道中的电荷进行控制,通过调节栅极电压来调整沟道的导电性。

2、运算放大器

运算放大器是一种有源器件,通常用于信号放大和运算电路中。它由多个晶体管和被动元件组成,具有一个非常高的开环增益。运算放大器通常被设计为差分放大器,具有两个输入端(正向输入和反向输入)和一个输出端。

运算放大器可以根据不同的电路连接方式实现各种功能,如比较、滤波、积分、微分和放大等。它们广泛应用于模拟电路、信号处理、控制系统和通信系统等领域。

二、场效应管和mos管的区别

虽然mos管是场效应管的一种类型,但它们之间存在一些差异。下面将详细介绍场效应管和mos管之间的区别。

1、结构

场效应管:场效应管是一类半导体器件,包括了mos管。除了mos管外,场效应管还包括JFET(结型场效应管)和IGBT(绝缘栅双极型晶体管)等。

mos管:mos管是场效应管的一种类型,是最常见和广泛使用的场效应管。它由金属栅极、氧化物绝缘层和半导体通道组成。

2、工作原理

场效应管:场效应管的工作原理基于沟道中的电荷控制。通过调节栅极电压,可以改变沟道中的电荷密度,从而改变沟道的导电性。

mos管:mos管是一种以金属-氧化物-半导体结构为基础的场效应管。它利用氧化物绝缘层来隔离栅极和沟道之间的电荷,从而实现更好的控制。

三、应用领域

场效应管:JFET广泛应用于高频放大器、开关和稳压器等领域。

mos管:mos管是最常见的场效应管类型,广泛应用于数字和模拟电路中。它们在逻辑门、存储器、微处理器和功率放大器等领域发挥着重要作用。

1、特性和优势

场效应管:场效应管具有高输入阻抗、低输出阻抗和较低的噪声水平。JFET在低频应用中表现出色,并且具有较高的增益和较低的失真。

mos管:mos管具有高度集成、低功耗和快速开关特性。CMOS技术结合了N型MOS和P型MOS管道,提供了更低的功耗和更高的集成度。

理解mos管和运算放大器之间的区别对于正确选择和使用电子器件至关重要。根据具体的应用需求和电路设计,我们可以选择适合的器件来实现所需的功能和性能。

在线留言询价

如何区分MOS管的三个极

一文了解MOS管

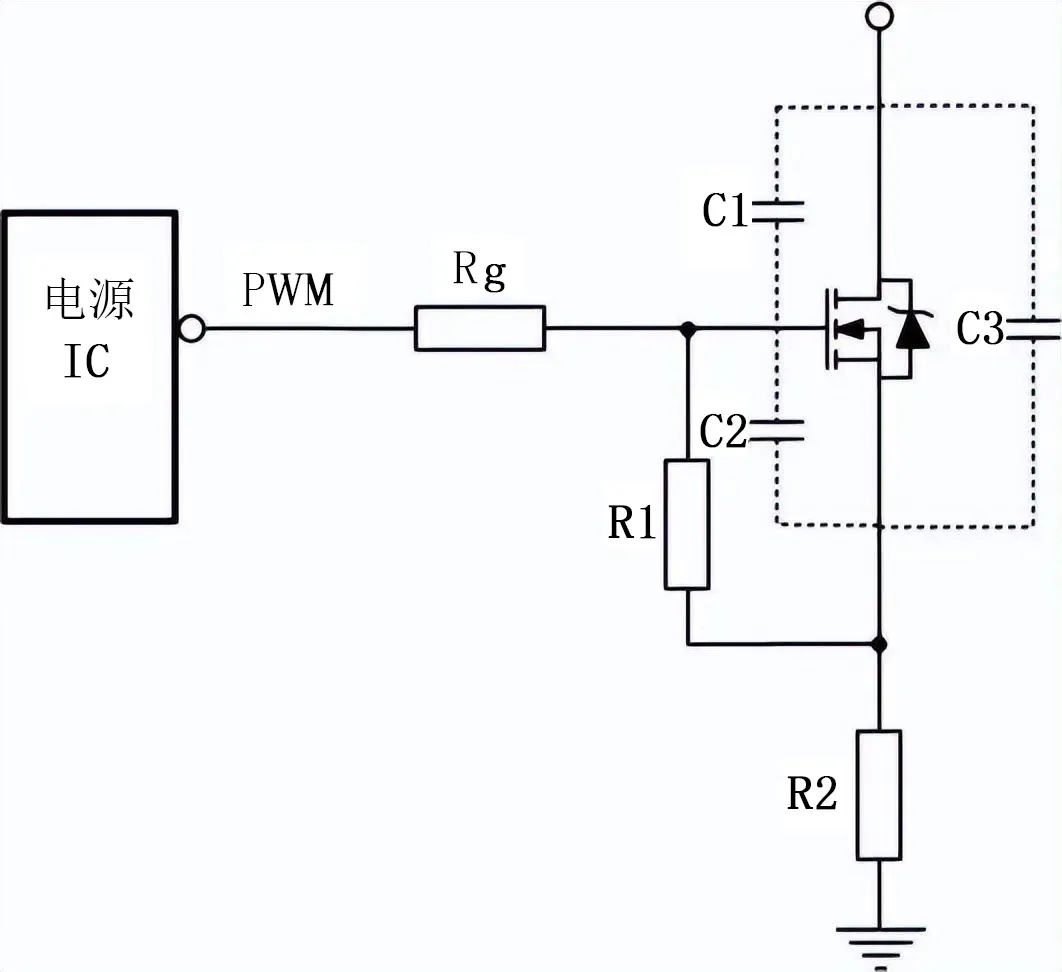

一文了解常见的几种MOS管驱动电路

- 一周热料

- 紧缺物料秒杀

| 型号 | 品牌 | 询价 |

|---|---|---|

| MC33074DR2G | onsemi | |

| TL431ACLPR | Texas Instruments | |

| RB751G-40T2R | ROHM Semiconductor | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| CDZVT2R20B | ROHM Semiconductor |

| 型号 | 品牌 | 抢购 |

|---|---|---|

| TPS63050YFFR | Texas Instruments | |

| STM32F429IGT6 | STMicroelectronics | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| BP3621 | ROHM Semiconductor | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| ESR03EZPJ151 | ROHM Semiconductor |

AMEYA360公众号二维码

识别二维码,即可关注

请输入下方图片中的验证码: