MOS管失效的六大原因

功率器件在近几年的市场方面发展的非常火爆,尤其是 MOS 管,他主要应用在电源适配器,电池管理系统以及逆变器和电机控制系统中。

而随着计算器主板,AI 显卡,服务器等行业的爆发,低压功率 MOS 管将再次迎来爆发性的市场需求。

在开关电源应用领域,由于电源的 Controller 做的已经非常完善,且大部分 Controller 为纯硬件控制,厂家一般也会对布局布线和 MOS 的驱动做专门的优化,因此在开关电源应用中的 MOS 烧坏的情况比较少,大部分表现为过热。

而在电池管理系统,和电机控制系统以及逆变器系统中,MOS 管的烧坏概率就变得非常大,其原因在于,电池管理系统的保护瞬间电流突变,电机和逆变器系统中的 MOS 带载都是非常大的感性负载,尤其是电机控制还面临着制动带来的反向电动势,都对 MOS 管的工作电压和电流提出了更大的挑战。

今天我们趁热打铁,分析一下 MOS 管最常见的 6 个失效模式。

失效模式 雪崩失效雪崩失效指的就是过压击穿,也就是我们常常说的漏极和源极之间的电压超过了 MOSFET 的额定电压,并且达到了 MOSFET 耐受的极限,从而导致 MOSFET 失效。

SOA 失效SOA 失效指的是过流损坏,也就是说,电流超过了 MOSFET 的安全工作区引起的失效,一般是由于 Id 超过了器件规格测定的最大值,使得 MOSFET 的热损耗过大,长期热量累积而导致的失效。

静电失效静电失效比较好理解,几乎任何电子元器件都面临静电问题,尤其是在北方干燥的冬天。要知道,MOS 管的一般静电耐受是 500V,非常的脆弱,所以冬天我们在操作 MOS 管的时候还是尽量使用防静电手环和镊子。

栅极击穿栅极击穿指的是栅极遭受异常电压导致栅极栅氧化层失效,一般我们驱动 MOS 管的 Vgs 设定在 12V,器件手册中虽然标注了 Vth 一般在 2-5V,但是对于不同的 Vgs 会对应不同的 Rdson,因此我们通常选用 12V 或者 15V 来保证 MOSFET 的完全开启。而这个电压并不能像 MOS 的 Vds 一样具备很高的耐电压能力,Vgs 一般会被限制在 20V 以内,超过 20V 将有可能击穿栅极。

栅极击穿后,一般使用万用表可以测量出来,GS 之间短路,而 DS 之间正常成高阻态。

谐振失效无论是电池管理系统,还是逆变器和电机控制领域,我们通常会使用 MOS 的多并联设计,由于 MOSFET 本身参数的不一致性会导致每个 MOSFET 的栅极及电路寄生参数不同,在一同开关的时候,由于开通的先后顺序问题引起开关震荡,进一步损坏MOSFET,因此在并联使用的时候一定要注意布局布线,以及 MOS 的Vth 选择和供应链管理,这一点我将专门另一起篇文章讨论。

体二极管失效在电机控制,桥式整流和 LLC 等控制系统中,我们需要利用 MOSFET 的体二极管进行续流,一般情况下体二极管的反向恢复时间会比较慢,因此容易出现过功率而导致体二极管失效。因此一般控制频率比较高的系统中,我们需要在 MOSFET 外面并联一个快恢复二极管或者肖特基。下面,我们就过压击穿和过流烧毁再详细分析一下它的失效过程和预防措施

雪崩失效及其预防

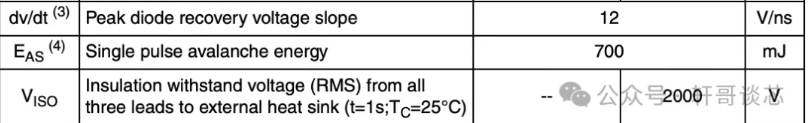

简单来说,MOSFET 在电源板上由于母线电压,变压器反射电压,电机的反向电动势,漏感尖峰电压等等系统中的高压交叠之后,都将叠加在 MOSFET 的漏源极之间。MOSFET 的手册中一般会包含单面冲雪崩能量 Eas、重复脉冲雪崩能量 Ear 和单次脉冲雪崩电流 Ias 等参数,这些参数反映了该功率 MOSFET 的雪崩能力。

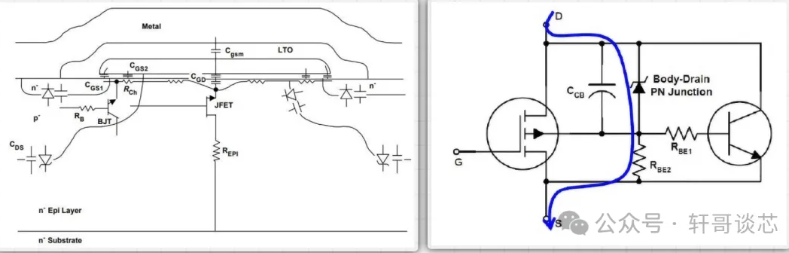

其实在实际的 MOSFET 中还存在着一个寄生的三极管,就像漏源极之间的续流二极管一样,可以看下面的内部示意图和对应的等效电路图:

我们可以看到,这个寄生的 BJT 是直接并联在 MOSFET 上面的,因此,当 MOSFET 漏极存在一个大电流 Id 和高压 Vd 时,器件内部的电离作用加剧,出现大量的空穴电流,这些电流流过 Rb 电阻进入源极就导致了寄生三极管的基极电势升高,也就是 Vb 会升高,那么寄生三极管就会导通,从而发生雪崩击穿,所以,其内部是由于过压产生了电流流入了寄生三极管,三极管导通了,就等于 MOSFET 也导通了。

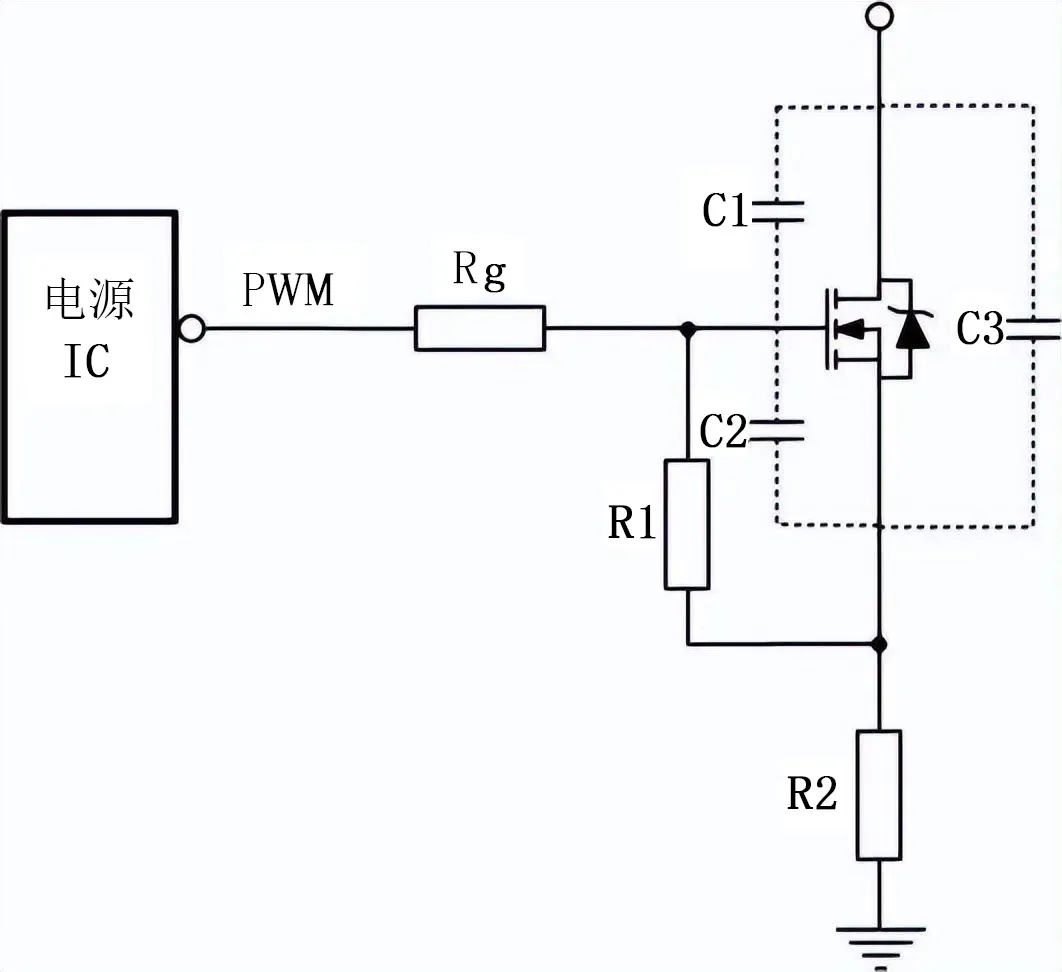

预防的措施:雪崩失效归根结底是电压失效,因此预防我们着重从电压来考虑。具体可以参考以下的方式来处理。1:合理降额使用,目前行业内的降额一般选取80%-95%的降额,具体情况根据企业的保修条款及电路关注点进行选取。2:合理的变压器反射电压。3:合理的RCD及TVS吸收电路设计。4:大电流布线尽量采用粗、短的布局结构,尽量减少布线寄生电感。5:选择合理的栅极电阻Rg。6:在大功率电源中,可以根据需要适当的加入RC减震或齐纳二极管进行吸收。

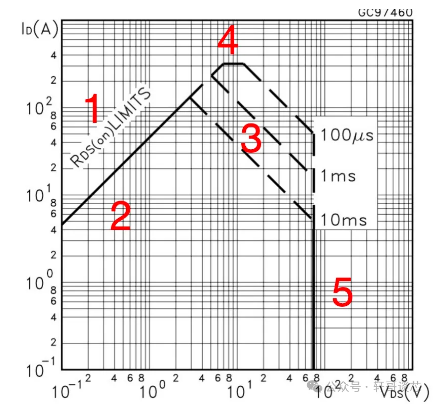

SOA失效机器预防SOA失效是指电源在运行时异常的大电流和电压同时叠加在MOSFET上面,造成瞬时局部发热而导致的破坏模式。或者是芯片与散热器及封装不能及时达到热平衡导致热积累,持续的发热使温度超过氧化层限制而导致的热击穿模式。关于SOA各个线的参数限定值可以参考下面图片,每个 MOSFET 的数据手册里面都有。

下面我们分析下图中标注的 5 个区域的含义

这个地方主要限制最大的额定电流和脉冲电流,因为此刻的横轴显示电压很低,那么更多的是大电流导致的 SOA 失效。

在 2 的区域内属于电流电压都安全的区域,但是也要看器件的结温(取决于 Rdson 大小),如果结温超过了 150 度,也会导致 SOA 失效。

在 3 号区域内,我们可以看到根据不同的时间被扩展了三次,分别对应着 10ms,1ms 和 100us,这里主要看器件的耗散功率,本质上是能够承受住 10ms 的最大电流值。

在 4 号区域,这是一个电流值封顶的区域,这里指的就是脉冲电流的最大值的限制,超过了就会导致 SOA 失效。

在 5 号区域,这是一个电压的封顶区域,这里主要限制 Vds 上的电压。

我们电路中的MOSFET,只要保证能器件处于上面限制区的范围内(2 和 3),就能有效的规避由于MOSFET而导致的电源失效问题的产生。预防措施:

确保在最差条件下,MOSFET的所有功率限制条件均在SOA限制线以内。

将OCP功能一定要做精确细致。在进行OCP点设计时,一般可能会取1.1-1.5倍电流余量,然后就根据IC的保护电压比如0.7V开始调试RSENSE电阻。另外有些MOSDriver 还集成了过流保护功能,也可以尝试,就是贵。

合理的热设计冗余也是非常必要的,对于额定电流和最大电流工作时间的可靠性测试必不可少,记得叠加上工作环境温度。

Previous:罗姆集团旗下的SiCrystal与意法半导体扩大SiC晶圆供应合同

Online messageinquiry

如何区分MOS管的三个极

一文了解MOS管

一文了解常见的几种MOS管驱动电路

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| TL431ACLPR | Texas Instruments | |

| CDZVT2R20B | ROHM Semiconductor | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| RB751G-40T2R | ROHM Semiconductor | |

| MC33074DR2G | onsemi |

| model | brand | To snap up |

|---|---|---|

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| BP3621 | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics | |

| TPS63050YFFR | Texas Instruments | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| BU33JA2MNVX-CTL | ROHM Semiconductor |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: