- Ameya360 Component Supply Platform >

- Trade news >

- 多个MOS管并联应用场景的四大要点

多个MOS管并联应用场景的四大要点

功率MOS管具有优异的热稳定性,不会发生热失控,因此 并联多个MOSFET是一种很常见的使用方法,它可以减少传导损耗和分散功耗,以便限制最大结温。

1.功率MOS并联要点

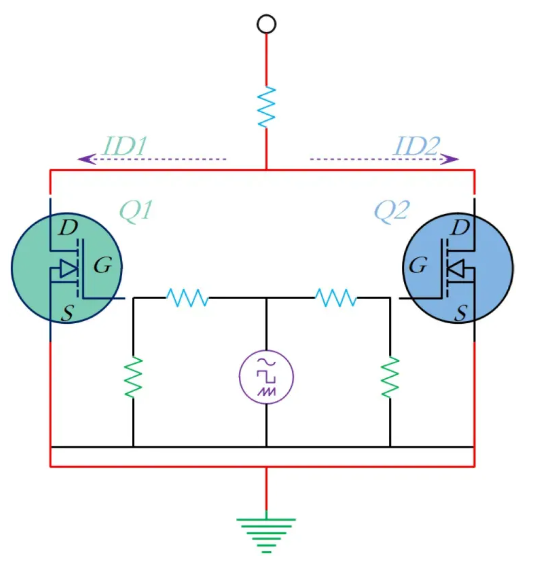

在高速下空中高功率下,进行并行连接时,最主要的是需要避免电流集中,以及过电流,能够确保在所有可能的负载条件下,很好地平衡、均匀所有流过器件的电流。

2.功率MOS并联时的静态/动态动作

静态:

Rds(on)较低的MOS管能够导通更多的电流。

当它升温时,Rds(on)增加,部分电流将转移到其它MOS管上,电流共享取决于每个MOS的相对的电阻值。

注意:a.每个MOS的电流与其接通电阻的Rds(on)的倒数成正比关系;

b.热耦合良好的平行放置MOS的结温度大致相同。

动态:

动态运行时,阈值电压Vgsth最低的MOS管首先打开,最后关闭。这种MOS管一般会占据更多的开关损耗,并且在开关转换过程中,承担了更高的电应力。

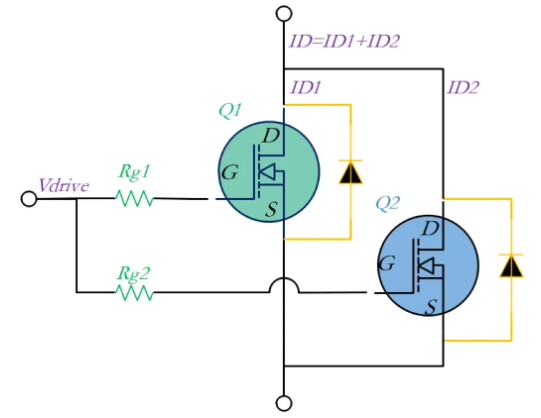

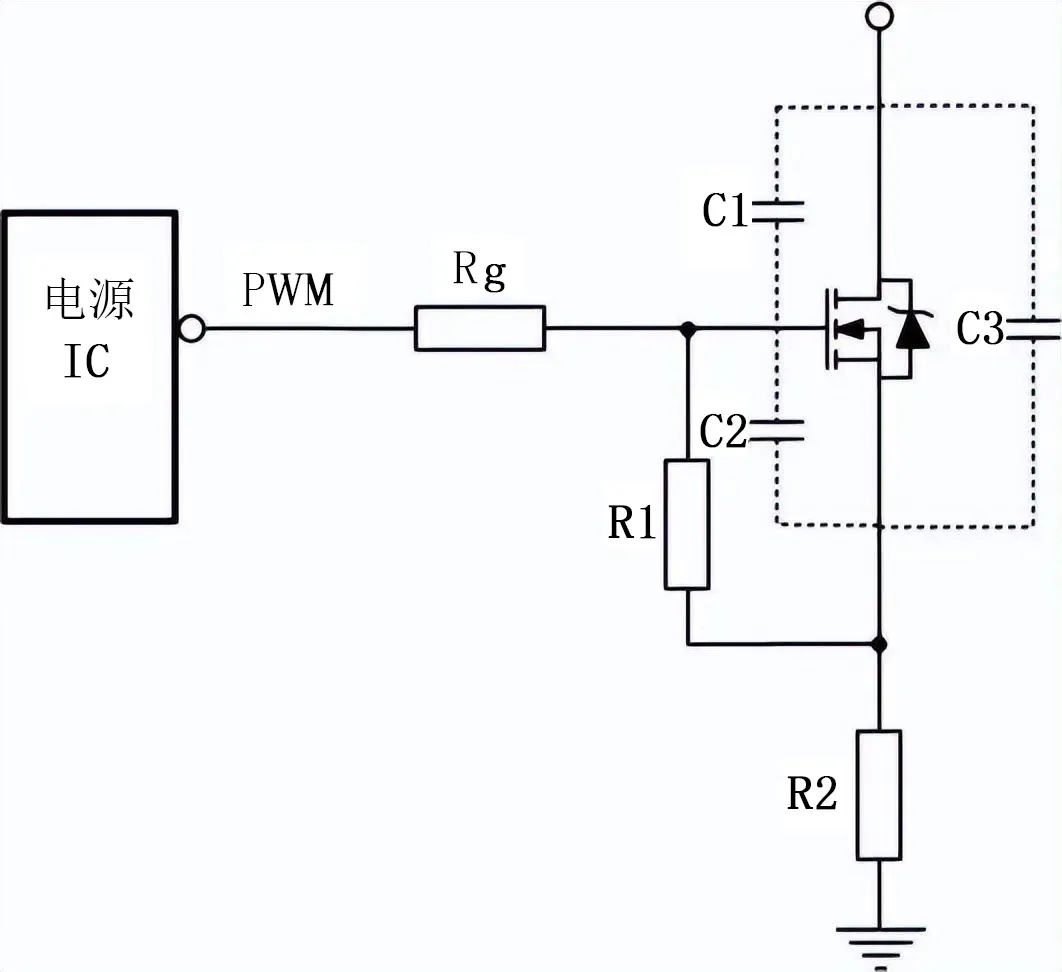

3.开启、关断阈值保持一致

由于功率MOS切换时间会有所差异,因此在通电和断电期间容易出现不平衡,而在开关时间上的变化很大程度是由门-源阈值电压Vth的值。即:Vth的值越小,通电时间越快。相反,断电期间,Vth的值越大,截止的速度就越快。

此外,当电流集中在一个具有较小Vth的功率MOS上时,通电与断电的过程中会出现电流不平衡,这会让设备功率损耗过大,导致故障。因此,最好使用相近Vth值以及开关时间的变化,在每个MOS之间插入一个电阻,可以确保稳定运行以及防止异常振荡。

4. 其他要点

A.每个MOS需要栅极电阻,且阻值在几Ω到几十Ω,防止电流共享和振荡;

B.MOS管具备良好的热耦合,确保电流和热平衡;

C.避免在GS之间添加外部器件,可以适当调整电阻值,优化开关速度。

问题来了,那并联多个双极晶体管和MOS管有什么主要区别吗?

双极晶体管由于是基极电流驱动,因此电流平衡更容易被基极-发射极电压Vbe的波动所破坏,这样会导致并联连接均衡会变得困难。

而功率MOS管,由于是电压驱动,因此只需要向并联连接的每个MOS管提供驱动电压就可以保持相当不错的均衡性,使并联更加容易,因此MOS管相比双极晶体管,在多个并联的场景中会更有优势。

Previous:日系被动元件大厂计划涨价20%!

Online messageinquiry

如何区分MOS管的三个极

一文了解MOS管

一文了解常见的几种MOS管驱动电路

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| CDZVT2R20B | ROHM Semiconductor | |

| RB751G-40T2R | ROHM Semiconductor | |

| MC33074DR2G | onsemi | |

| TL431ACLPR | Texas Instruments | |

| BD71847AMWV-E2 | ROHM Semiconductor |

| model | brand | To snap up |

|---|---|---|

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments | |

| STM32F429IGT6 | STMicroelectronics | |

| BP3621 | ROHM Semiconductor | |

| ESR03EZPJ151 | ROHM Semiconductor |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: