核芯互联推出CLF04828:超低噪声去抖时钟

随着现代电子系统对高精度、高可靠性时钟信号需求的不断提升,时钟抖动成为影响系统性能的关键因素。核芯互联科技有限公司重磅推出CLF04828超低噪声去抖时钟,凭借其领先的双PLL架构、超低相位噪声和灵活的输出配置,为多领域高性能应用提供了强大的技术支持。

产品亮点解析:性能与灵活性的完美结合

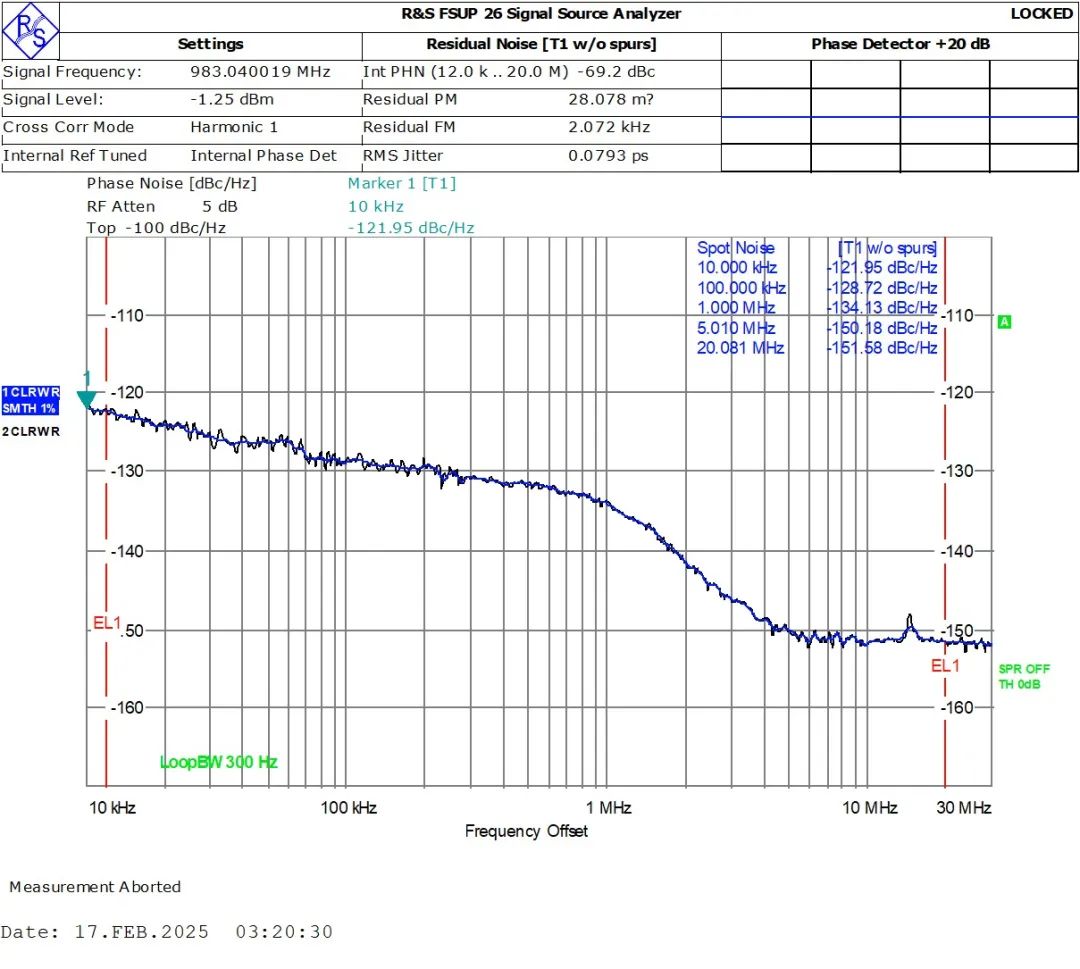

1. 超低抖动与噪声性能79 fs RMS抖动(12 kHz到20 MHz积分):极大降低信号失真和误码率,提升系统稳定性。

-161 dBc/Hz底噪(245.76 MHz下):在高频应用中展现卓越的信号完整性,特别适合对相位噪声敏感的通信和测量设备。

2. 强大的输出能力14路差分时钟输出,支持最多7路SYSREF时钟,满足复杂系统的多路同步需求。

最高输出频率达2.7 GHz,支持LVPECL、LVDS等多种接口标准,适配不同场景。

输出支持1到32的整数分频,和32bit小数分频,并具备50%占空比,提供灵活的频率配置。

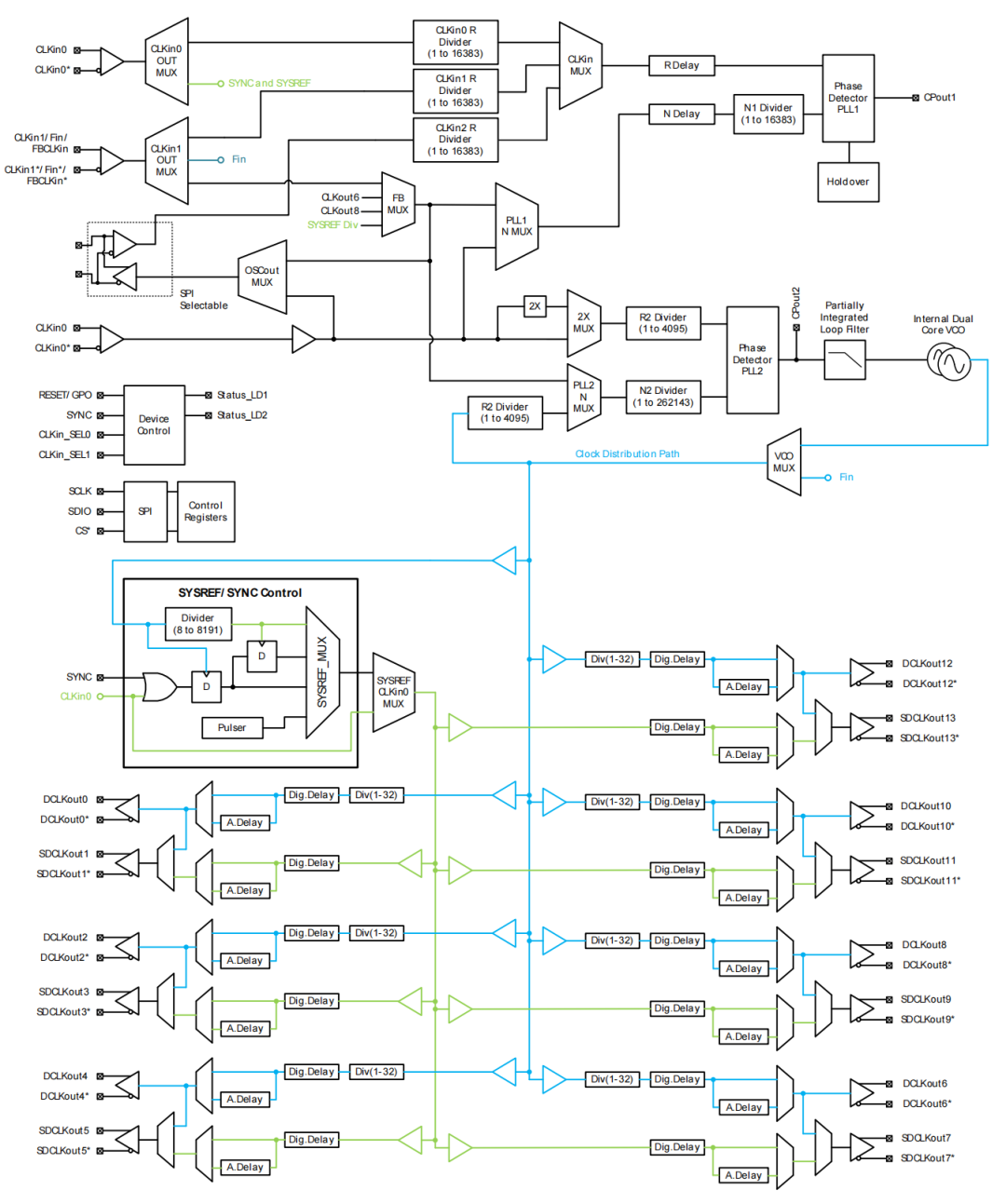

3. 灵活的工作模式双PLL模式:通过第一级PLL实现抖动消除,第二级PLL提供高性能时钟输出。

0延迟模式:实现输入与输出信号的相位同步,支持确定性延迟设计。

保持模式(Holdover):在输入时钟丢失时,保持输出时钟的稳定性,确保系统连续运行。

4. 高精度延迟调节支持40 ps步进的模拟延迟和高精度数字延迟,满足对时钟相位的精确控制需求。

5. 高可靠性设计宽工作温度范围:-40℃至85℃,适应严苛的工业环境。

QFN-64封装:优化的热性能设计,确保芯片在高功耗场景下的稳定运行。

典型应用场景:赋能多行业技术创新

CLF04828以其卓越的性能和灵活性,广泛适用于以下领域:

1. 无线通信基础设施支持JEDEC JESD204B标准,为5G基站、雷达通信等应用提供高精度时钟同步,提升数据传输效率。

2. 数据中心与高性能网络设备适配SONET/SDH、DSLAM等网络协议,优化时钟分配,确保大规模数据处理的稳定性。

3. 医疗与视频设备高精度时钟同步提升医疗影像设备的分辨率和处理速度,同时助力高品质视频设备实现流畅播放。

4. 测量与测试仪器提供高稳定性时钟源,满足精密测量和测试设备对低噪声、高精度的苛刻要求。

技术优势:领先市场,超越竞品

与市场上的同类产品相比,CLF04828在以下方面展现了显著优势:

1. 极致的低抖动性能在12 kHz到20 MHz范围内,79 fs RMS抖动优于市场主流产品,显著降低误码率,提升信号完整性。

2. 灵活的输出配置支持14路差分输出,涵盖LVPECL、LVDS等主流接口,适配多种应用场景,降低客户设计复杂性。

3. 多样化的工作模式提供双PLL、0延迟、保持模式等多种配置,满足从通信到医疗的广泛需求。

4. 高可靠性与宽温范围工作温度范围达-40℃到85℃,适应严苛的工业环境,确保产品在极端条件下稳定运行。

5. 全国产化方案设计、流片、封装均在大陆境内完成,采用全国产化方案。

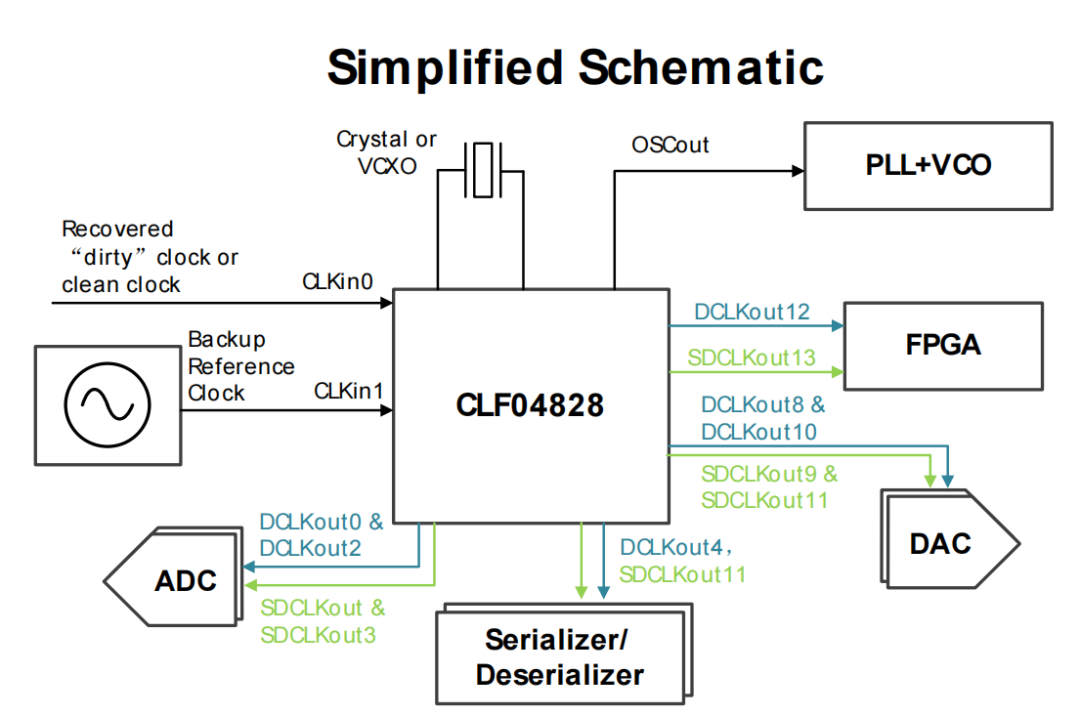

典型应用电路:助力系统设计以下为CLF04828的典型应用电路,展示其在FPGA、DAC、ADC等系统中的连接方式:

双PLL架构第一级PLL通过窄带环路实现抖动消除,第二级PLL提供高性能输出。

内部VCO驱动多达7个分频/延时模块,可灵活配置14路输出。

0延迟模式实现输入与输出信号的相位同步,支持确定性延迟设计,适用于需要高同步精度的系统。

保持模式在输入时钟丢失时,保持输出时钟的稳定性,确保系统连续运行。

测试结果:卓越性能一览在实际测试中,CLF04828展现了卓越的性能:

245 MHz时的相位噪声:-161 dBc/Hz,领先市场同类产品。

983 MHz、1.97 GHz等频率下的输出:无论LVDS还是LVPECL接口,均表现出极低的抖动和噪声。

在线留言询价

- 一周热料

- 紧缺物料秒杀

| 型号 | 品牌 | 询价 |

|---|---|---|

| CDZVT2R20B | ROHM Semiconductor | |

| RB751G-40T2R | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| MC33074DR2G | onsemi |

| 型号 | 品牌 | 抢购 |

|---|---|---|

| ESR03EZPJ151 | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments | |

| BP3621 | ROHM Semiconductor | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| STM32F429IGT6 | STMicroelectronics |

AMEYA360公众号二维码

识别二维码,即可关注

请输入下方图片中的验证码: