- Ameya360 Component Supply Platform >

- Trade news >

- 金属材料变革,中国半导体设备研发方向将受影响

金属材料变革,中国半导体设备研发方向将受影响

全球最大半导体设备商应用材料(Applied Materials)于2018年6月6日宣布,在材料工程上获得技术突破,能在大数据与人工智能(AI)时代加速芯片效能。

Applied Materials表示,20年来首桩晶体管接点与导线的重大金属材料变革,能解除7nm及以下晶圆制程主要的效能瓶颈,由于钨(W)在晶体管接点的电性表现与铜(Cu)的局部终端金属导线制程都已经逼近物理极限,成为FinFET无法完全发挥效能的瓶颈,因此芯片设计者在7nm以下能以钴(Co)金属取代钨与铜,借以增进15%的芯片效能。

采用钴可优化先进制程金属填充情形,延续7nm以下的制程微缩

钨和铜是目前先进制程所采用的重要金属材料,然而钨和铜与绝缘层附着力差,因此都需要线性层(Liner Layer)增加金属与绝缘层间的附着力。

此外,为了避免阻止钨及铜原子扩散至绝缘层而影响芯片电性,必须有阻挡层存在。

如下图所示,随着制程微缩至20nm以下,以钨 contact制程为例,20nm的Contact CD中,Barrier就占了8nm,Contact中实际金属层为12nm (金属填充8nm+ 晶核形成 4nm),Contact直径为10nm时,实际金属层仅剩2nm,以此估算Contact直径为8nm时将没有金属层的容纳空间,此时线性层及阻挡层的厚度成了制程微缩瓶颈。

注:金属导线及晶体管间的连接通道称为Contact,由于Contact实际形状是非常贴近圆柱体的圆锥体。因此Contact CD一般指的是Contact直径

注:图中Barrier包含Barrier Layer+Liner Layer

W Contact的金属填充情形;source:Applied Materials

然而同样10nm的Contact直径若采用钴(如下图),其Barrier仅4nm,而实际金属层则有6nm,相较于采用钨更有潜力在7nm以下制程持续发展。

注:图中Barrier包含Barrier Layer+Liner Layer

CO Contact的金属填充情形;source:Applied Materials

金属材料变革将影响中国半导体设备的研发方向

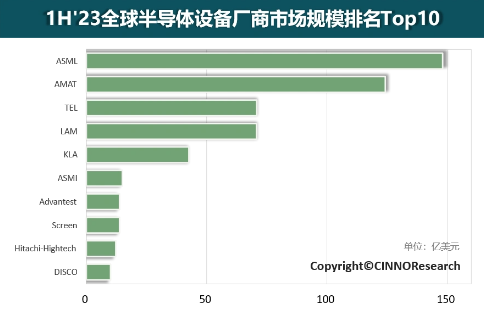

目前中国半导体设备以蚀刻、薄膜及CMP的发展脚步最快,此部分将以打入主流厂商产线、取得认证并藉此建立量产数据为目标,朝向打入先进制程的前段晶体管制程之远期目标是相当明确。

然而相较于国际主流半导体设备厂商的技术水平,中国半导体设备厂商仍是追随者角色,因此钴取代钨和铜的趋势确立,将影响中国半导体设备厂商尤其是蚀刻、薄膜及CMP的研究发展方向。

Previous:传华新科,三星MLCC 7月涨价

Online messageinquiry

一文带你看完国产半导体设备厂商

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| RB751G-40T2R | ROHM Semiconductor | |

| CDZVT2R20B | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments | |

| MC33074DR2G | onsemi | |

| BD71847AMWV-E2 | ROHM Semiconductor |

| model | brand | To snap up |

|---|---|---|

| STM32F429IGT6 | STMicroelectronics | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| TPS63050YFFR | Texas Instruments | |

| BP3621 | ROHM Semiconductor |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: