MOSFET的基本结构与工作原理

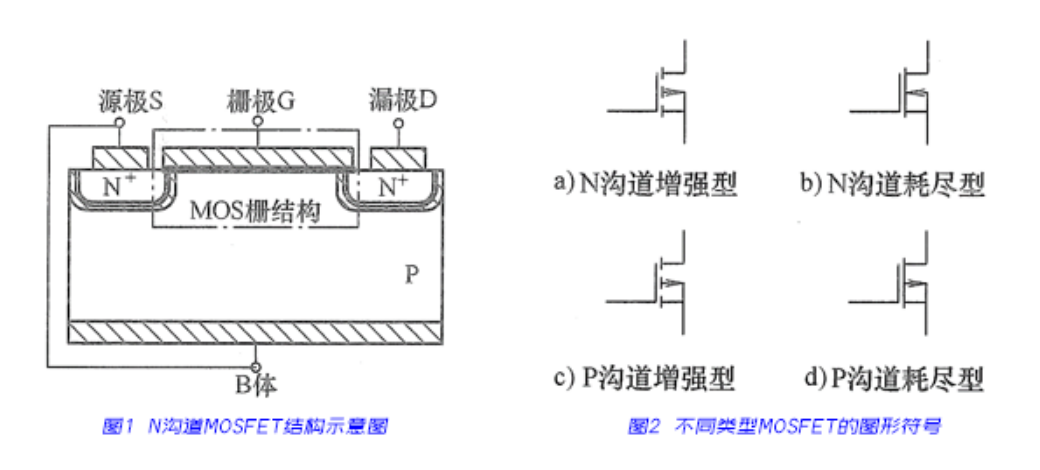

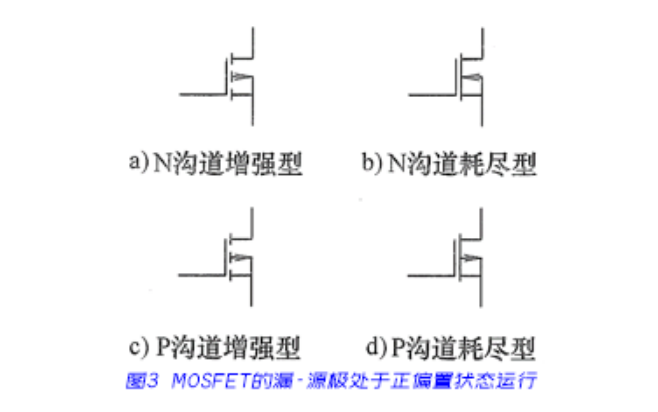

MOS栅结构是MOSFET的重要组成部分,一个典型的N沟道增强型结构示意图如图1所示。其中栅极、源极和漏极位于同一个平面内,半导体的另一个平面可以称为体端,所以在一些书籍和资料中,也将MOSFET称为四端器件,实际上那个体端一般跟源极相连接,所以在此还是将MOSFET看成三端器件。N沟道增强型MOSFET的图形符号如图2a所示,跟结型场效应晶体管一样,存在3种类型的MOSFET,它们的图形符号如图2b、c和d所示。在实际应用中,一般不特指时的MOSFET都是增强型MOSFET,即在栅极不控制时,漏极-源极之间可以承受正偏置电压。

在图1中,点划线框内就是典型的MOS结构,或者称为MOS栅结构。在金属和P型半导体之间的黑色部分就是氧化物绝缘层。需要补充说明的是,在早期的MOS栅结构中,金属侧只能使用金属材料,而在现代的MOS栅结构中,金属几乎完全被重掺杂的多晶硅或者金属-多晶硅合金所代替,这些材料在生产方便性和可靠性上都更具有优势。不妨碍对MOSFET结构和基本工作原理的理解,在此仍认为其是金属材料。和结型场效应晶体管一样,在MOSFET中载流子也是从源极经过沟道流向漏极,所以与源极和漏极相连接的都是重掺杂的N^+^区,以便更好地提供载流子。仔细观察,在MOSFET中,由于源极和体端相连接,从源极到漏极,即从体端到漏极还存在PN^+^结,即一个双极型二极管,显然它对 MOSFET的反向阻断和导通特性有明显的影响。

为分析和表述方便,定义栅极到源极(就是栅极到体端)的电压为UGS,漏极到源极的电压为UDS,流经MOSFET的电流,即流入漏极的电流为ID。

MOSFET的基本工作原理和特性主要体现在MOS结构的工作原理以及MOSFET中沟道的特性。此时要分两大类情况来分析MOSFET的基本工作原理,一类是MOSFET的漏-源极处于正偏置状态,另一类是漏-源极处于反偏置状态。

当MOSFET的漏-源极处于正偏置状态,即UDS>0时,体端到漏极的二极管处于反偏置状态,PN^+^结的空间电荷区主要是在P区内展宽,从漏极到源极存在一个很小的漏电流。此时当栅极电压即UGS逐渐增高时,MOS栅结构就会经历耗尽、弱反型和强反型三个阶段,分别如图3b、c和d所示。

在UGS刚大于零时,在氧化物绝缘层的下方P型半导体中出现了耗尽层,即空穴被门极电压产生的电场推开,留下受主离子;而当UGS增加到一定程度时,在氧化物绝缘层的下方的P型半导体中出现反型层,此时还处于弱反型阶段,即在反型层中有NA>>np>pp,载流子的浓度远小于半导体中受主原子的浓度,此时栅极电压并没有改变整个器件的导电特性。当UGS大于开启电压UT时,氧化物绝缘层的下方P型半导体中出现强反型层,在反型中有np>NA,此时的反型层中电子占优势,其导电行为主要是电子的漂移运动,形成从源极到漏极的电子流,即漏极到源极的电流ID,形成的强反型层称作沟道,根据其导电载流子性质,叫做N沟道(虽然在P型半导体中)。显然沟道的宽度和导电能力跟栅极电压有关,栅极电压越高,沟道的宽度和导电能力越强。可以认为,当栅极小于开启电压UT时,没有沟道形成。所以在MOSFET栅极零偏置时,MOSFET被关断,其间不会出现双极型器件因为储存载流子的抽出和复合而出现的开关延迟,其关断时间仅由MOS栅结构的电容放电时间决定,所以MOSFET相对于双极型器件来说,也是高开关频率器件。

以上就是MOSFET的漏-源极处于正偏置状态基本工作原理,还有必要关注MOSFET在通态时的特性,会出现与结型场效应晶体管一样的线性、过渡、饱和等区域。即MOS栅结构形成的沟道不但受栅极电压的影响,还受到漏-源之间电压的影响,由于沟道采用掺杂浓度不高的材料,其电阻率较高,当有电流在漏-源间流过时,其中必然出现压降。此时MOS栅结结构的偏置电压就不再均匀分布,MOS结构的空间电荷区的宽度从漏到源不再相等。

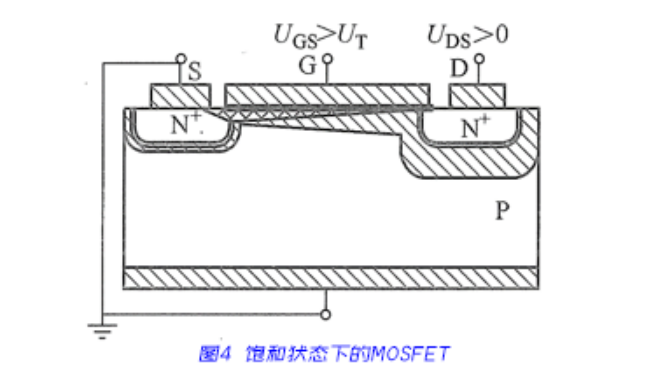

当流经电流较小时,电流在沟道中产生的电位梯度很小,沟道的外形几乎不发生改变,认为沟道是一个固定阻值的电阻区,则MOSFET的端电压和流经的电流之间呈线性关系。随着器件流经的电流增加,器件压降增加,沟道形状开始发生改变,且可看成是随压降变化的电阻,端电压和流经的电流关系就偏离线性关系。随着流经的电流和压降的进一步增加,出现图4所示的沟道一段被夹断的情况,此时压降增加而流经的电流不再增加,从而发生饱和,电子在强电场作用下通过夹断的沟道进入漏极来维持饱和电流。

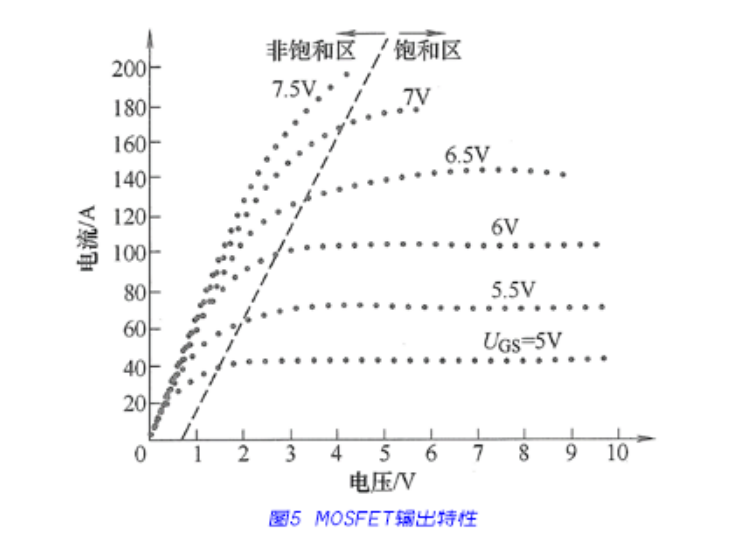

图5给出一个实际MOSFET在室温下的正偏置时输出特性曲线,即在不同的栅极电压情况下,MOSFET端电压与流经的电流的关系曲线族。图中是以实验点的形式给出,将线性区和过渡区合称为非饱和区。随着栅极电压的增加,非饱和区和饱和区的分界电压有所增加。由此可以看出,MOSFET的导电行为同时受到栅极电压和端电压的影响。

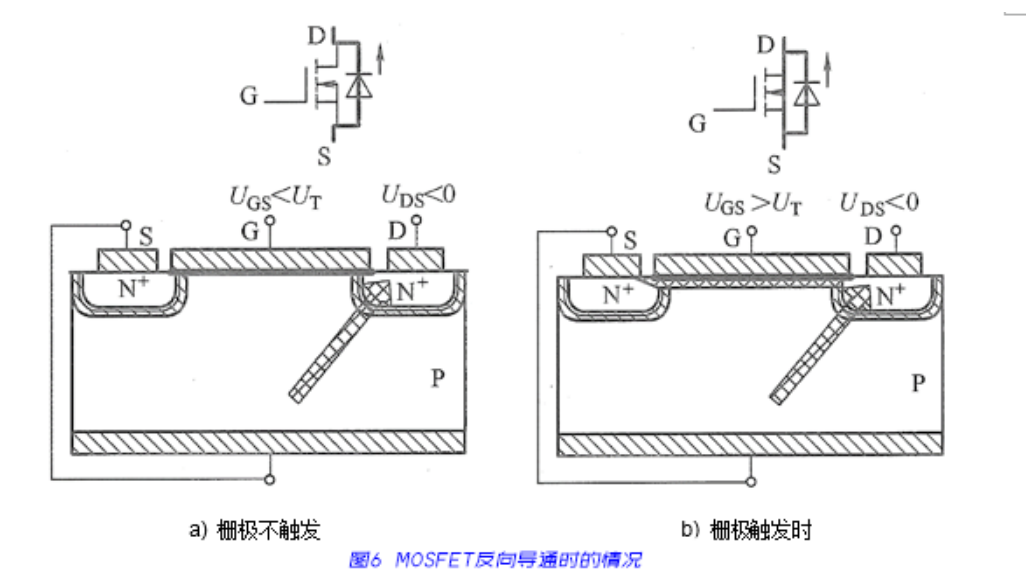

MOSFET的工作原理中,还有一类情况就是MOSFET的漏-源极处于反偏置状态,即UDS<0时的工作原理。此时体端到漏极的二极管处于正偏置状态,所以无论MOSFET的栅极电压如何变化,MOSFET都处于导通状态。只是导通的行为在不同情况下有所不同。存在两种情况:

·栅极电压UGS<ut时,mos栅结构中没有导电沟道的形成,mosfet的反向通态特性与一般的pn结二极管一样。

·栅极电压UGS>UT时,MOS栅结构中存在导电沟道,电子流可以从漏极流向源极,即电流可以从源极流向漏极,这部分的电流-电压特性关系可以看成图5所示的输出特性关于原点的对称。但是只要MOSFET的压降增加到一定程度,并联的PN结正偏置向P区注入电子,结果就会使MOSFET的反向导通特性变成二极管的导通特性。从电路的角度看,MOSFET反偏置状态可以看成MOS栅结构与PN结二极管的并联,两部分的电流-电压曲线不同,MOSFET总的反向导通特性取决于两者并联的均流关系。

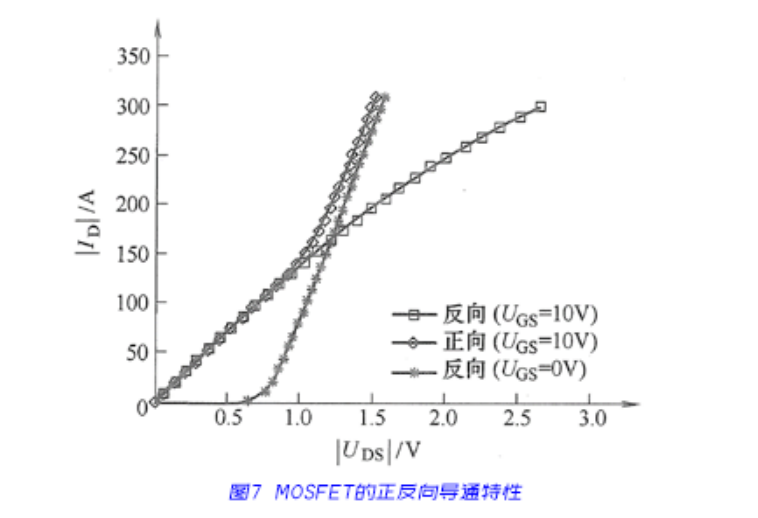

这两种情况的电流示意图如图6所示,图5所示的MOSFET的导通特性在绝对值坐标下的曲线关系如图7所示。

可以看出,在二极管没有导通的区域内,MOSFET在相同栅极电压下,正反向的电流-电压关系基本一致;栅极没有触发时,MOSFET的反向导通是双极型二极管特性;栅极触发时,MOSFET的反向导通是单极型的沟道特性与双极型二极管特性的分段组合。当然这种分段组合在低压大电流的功率MOSFET中体现得比铰明显,此时沟道区电阻阻值相对较低,在相当大小的电流范围内形成的压降比PN结的压降要小;对于一些高承压的MOSFET,沟道电阻阻值比较大,仅在非常窄的电流范围内形成的压降比PN结的压降小,几乎看不出分段组合。

在线留言询价

如何区分MOS管的三个极

一文了解MOS管

一文了解常见的几种MOS管驱动电路

耗尽型MOS管在LED照明中的应用

- 一周热料

- 紧缺物料秒杀

| 型号 | 品牌 | 询价 |

|---|---|---|

| TL431ACLPR | Texas Instruments | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| RB751G-40T2R | ROHM Semiconductor | |

| CDZVT2R20B | ROHM Semiconductor | |

| MC33074DR2G | onsemi |

| 型号 | 品牌 | 抢购 |

|---|---|---|

| ESR03EZPJ151 | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| BP3621 | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics | |

| BU33JA2MNVX-CTL | ROHM Semiconductor |

AMEYA360公众号二维码

识别二维码,即可关注

请输入下方图片中的验证码: