- Ameya360 Component Supply Platform >

- Trade news >

- 除了百度XPU/微软BrainWave,英伟达/AMD/瑞萨都在Hot Chips 2017上放大招

除了百度XPU/微软BrainWave,英伟达/AMD/瑞萨都在Hot Chips 2017上放大招

今年Hot Chips上和AI(包括自动驾驶)相关的内容(按会议的时间顺序)如下:

NVIDIA: Tutorial: "Building Autonomous Vehicles with NVIDIA’s DRIVE Platform"

The goal of this tutorial is to provide an overview of the autonomous vehicle landscape through NVIDIA’s platform and to highlight how deep neural networks are changing the autonomous vehicle landscape.

这个我没看到具体的内容,就不做评论了。

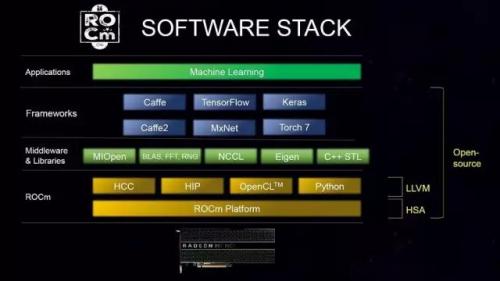

AMD: "AMD’s Radeon Next Generation GPU"

虽然这个presentation中直接涉及AI的内容不多,但有一张slide描述了一下AMD的Machie Learning software stack。

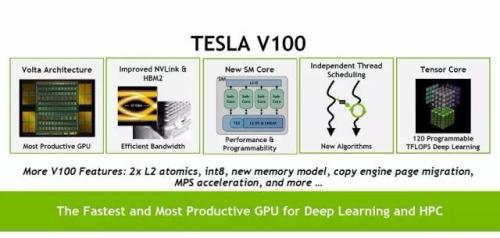

NVIDIA: "NVIDIA’s Volta GPU: Programmability and Performance for GPU Computing"

这个talk的大部分内容和5月发布Volta时的说明差不多,V100的几个主要特点包括:

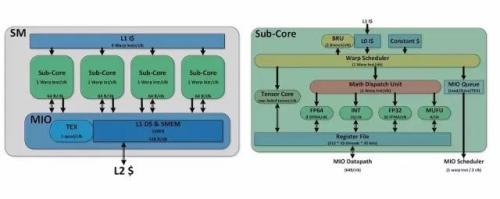

其中更详细的介绍了一下SM Core和Sub-Core的架构,如下图所示:

Wiseteachers.com: "The Direct Human/Machine Interface and hints of a General Artificial Intelligence"

Abstract: Dr. Alvelda will speak about the latest and future developments in Brain-Machine Interface, and how new discoveries and interdisciplinary work in neuroscience are driving new extensions to information theory and computing architectures.

这个内容看起来挺有意思,可惜没看到具体的材料。

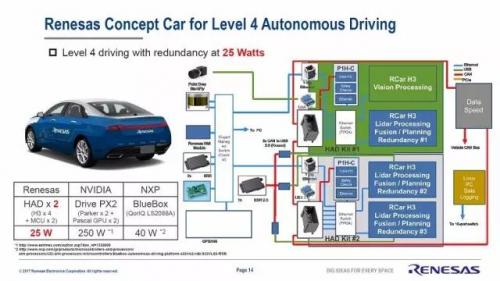

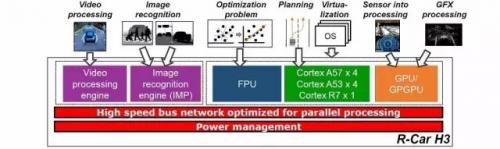

Renesas Electronics Corporation: "R-Car Gen3: Computing Platform for Autonomous Driving Era"

Renesas在汽车电子领域里做MCU是比较强的,这次推出的是一个完整的计算平台。从下图可以看出,它是和Nvidia的Drive PX2来竞争的。

而平台中的H3处理器是这个样子的:

Baidu: "XPU: A programmable FPGA Accelerator for diverse workloads"

这次百度的XPU大出风头,很多媒体都有报道。包括Nextplatform也有一篇文章介绍。我就不多说了。

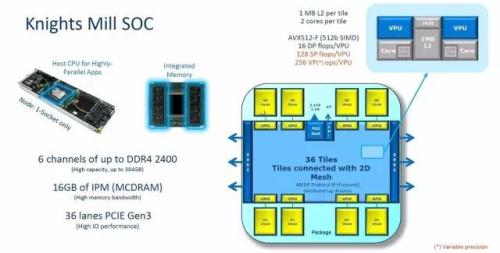

Intel: "Knights Mill: Intel Xeon Phi Processor for Machine Learning"

按Intel的说法,Knights Mill(KNM)是“First Knights product designed for Intel Scalable System Framework and targeted at Deep Learning”,它的DL Performance是KNL(Knights Landing)的4倍。(每次我总是想到King's Landing)

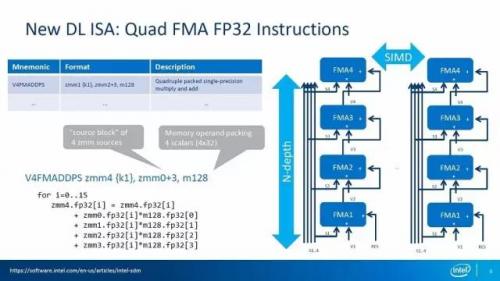

这个4倍是怎么得来的呢?首先,KNM增加了新的指令:

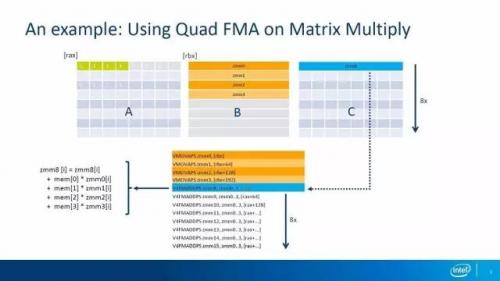

使用这个SIMD指令进行乘法运算的例子如下:

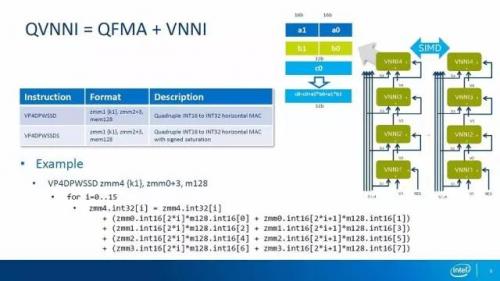

另外,KNM还引入了Variable Precision的概念。支持VNNI-16(Vector Neurual Network Instruction),输入INT16,输出INT32,可以并行实现两个16bit乘法并把结果累加到一个32bit的寄存器。VNNI和QFMA结合就有了如下指令:

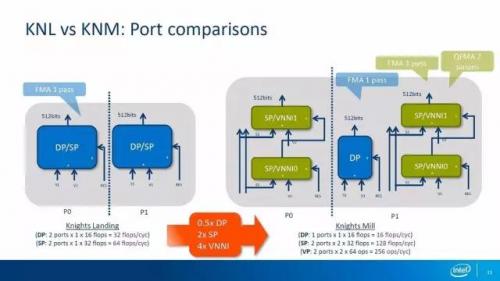

而从端口的角度可以看出KNM在双精度运算上比KNL慢了一倍,而在单精度和VNNI运算上则是KNL的2倍和4倍。

ThinCI: "Graph Streaming Processor (GSP) A Next-Generation Computing Architecture"

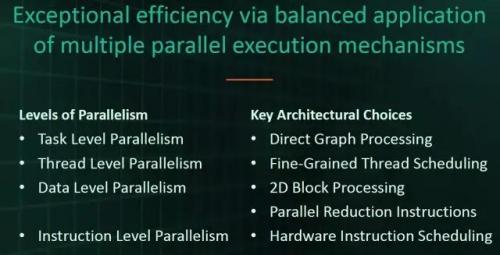

ThinCI这个Startup公司这次介绍了他们的GSP的架构设计目标:

总的来说,特色应该是Graph Processing。他们也介绍了他们实现Task Level, Thread Level, Data Level和Instruction Level并行的考虑。但是单从Slides来看也看不出太多细节,比较失望。如果有亲临现场听了的同学也欢迎留言介绍一下。

Wave Computing: "A Dataflow Processing Chip for Training Deep Neural Networks"

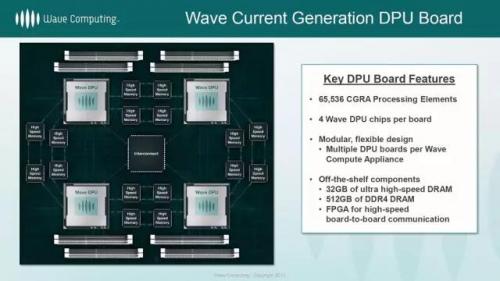

这次Wave Computing做的presentation还是比较细致的。不过,其中很多内容在之前这篇文章“AI芯片|浅析Yann LeCun提到的两款Dataflow Chip”里已经有了比较详细的说明。这里我们主要看一看比较新鲜的信息。首先是一个DPU Board的框图:

对此,Nextplatform的文章[1],中是这么介绍的

The graphic above shows four DPUs on a board with a cascading use of the HMC devices. The DPUs actually have quite a bit of interconnectivity through the HMCs, so if a dataflow graph is being executed, most of the communication is local from node to node in the graph. Wave lightly described a “balancing mechanism” to balance the delays through the execution of the graph via buffers between the nodes. By injecting some latency throughput is balanced through the graph and utilization increases. The tensor data for something like TensorFlow (native in the early access machines) is stored entirely in HMC, which means there is not much networking needed between the DPUs. In short, most of the data rides through the HMCs.

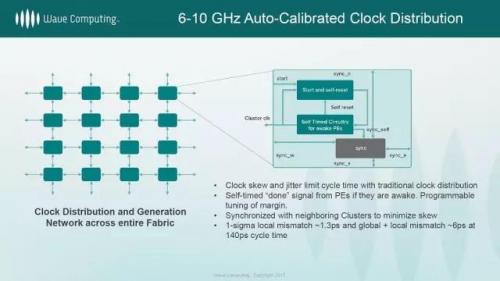

第二是时钟的设计。之前关注过Wave Computing的同学可能都会对他们的Clock-less设计印象深刻。他们使用这种技术使得1600多个PE和800多个Arithmetic Units可以工作在大约6.7GHz的频率。这次他们给出了这样的说明:

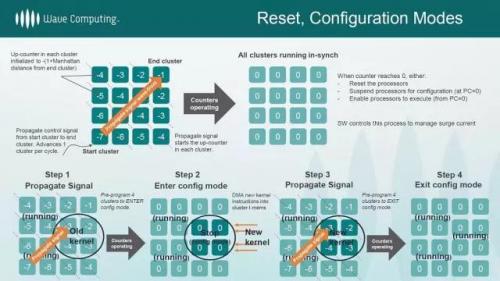

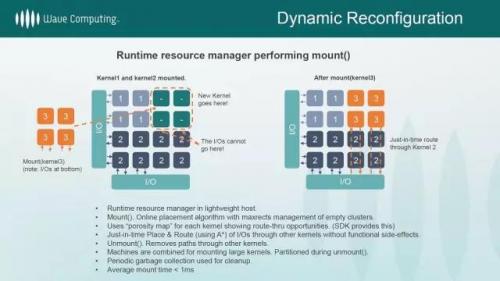

另外,这次他们还介绍了一下DPU是怎么实现Dynamic Reconfiguration的。

在众多xPU Startup公司当中,Wave Computing是很有技术特色的一个,值得大家关注。

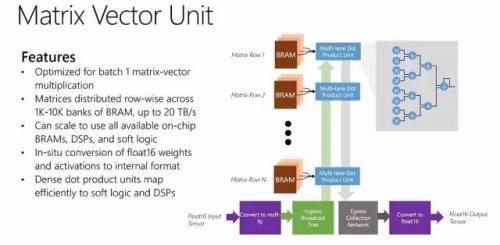

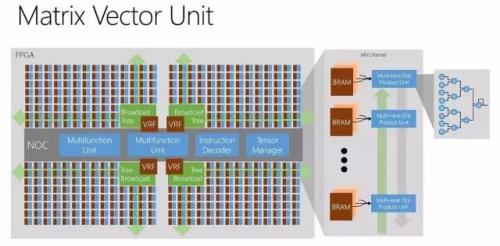

Microsoft: "Accelerating Persistent Neural Networks at Datacenter Scale"

微软在Cloud中使用FPGA加速的一些情况。这次微软的presentation内容更加丰富,值得好好看看。

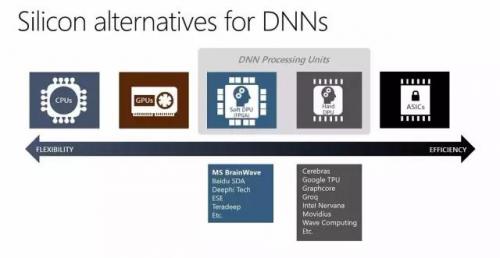

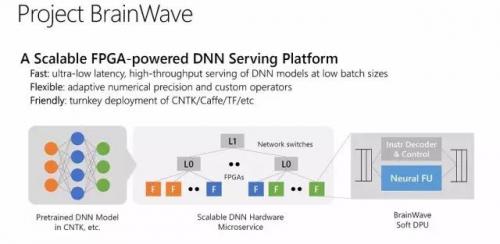

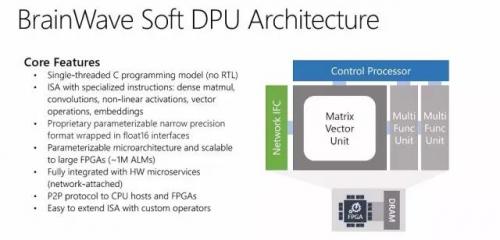

首先,这次微软提出了Soft DPU的概念,即在FPGA上实现DNN Processing Unit。并且列出了一些做Soft DPU的公司,包括百度和深鉴科技,以及做Hard DPU(ASIC)的公司(这里国内的公司还要争取知名度啊)。

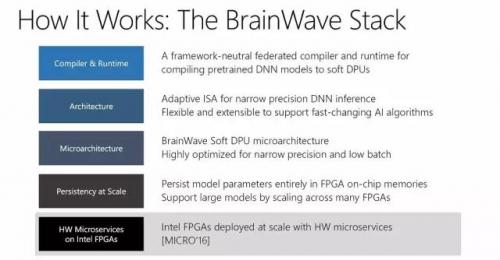

然后是正式提出BrainWave的名号,并介绍了它的完整Stack。

其中最底层的HW Microservice在我之前的文章中已经介绍过来,不再赘述。

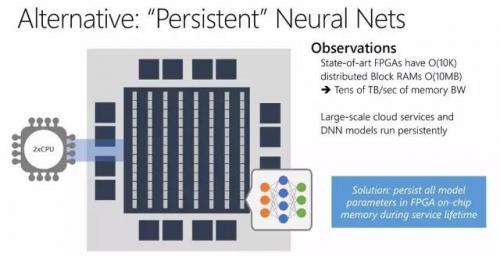

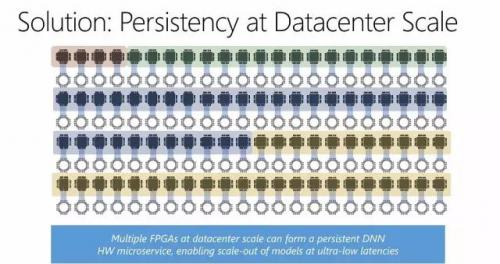

我们来看看上面几层。微软这次提出了一个“Persistent” Neural Net的概念。简单来说就是把model的所有参数都放在FPGA的on-chip memory当中。而不是我们常见的把参数放在片外的DRAM当中。这个想法似乎和GraphCore类似。

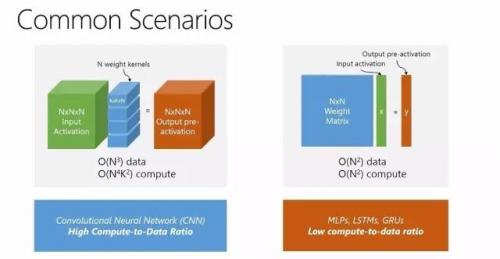

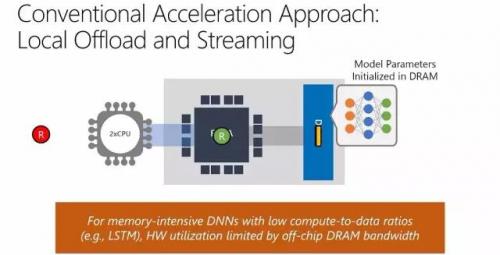

使用这种架构主要是基于下面的原因。

如果采用通常用来加速CNN的方法(模型参数存放于片外的DRAM),对于LSTM这类compute-to-data比率比较低的网络(相对于CNN),硬件的利用率将受限于off-chip DRAM的带宽。其实,这也是我们看到很多硬件加速器实现CNN效果很好,但对LSTM效率较低的原因之一。所以,微软提出的这个架构,对于特定网络可能有更好的效果,甚至可能好于ASIC。更进一步,在微软的Cloud FPGA架构下,还可以实现multi-FPGA的大规模Persistent Neural Net。当一个NN model在一个FPGA中放不下的时候,还可以这么玩儿。

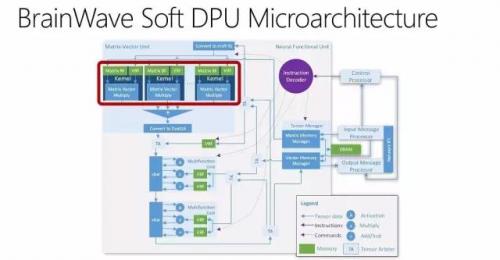

这次微软还给出了Soft DPU的Architecture和Micro-Architecture,干货不少,大家自己体会吧。总的来说,FPGA的可重复编程的特性可以给我们很大的想象空间。

最后是compiler和runtime,之前的文章“Deep Learning的IR“之争””也提过了。

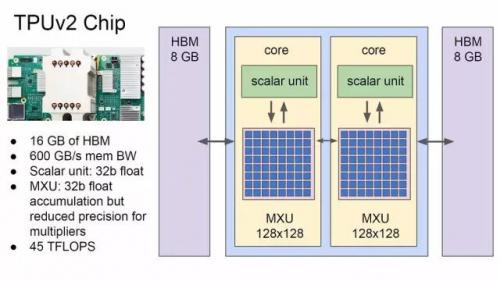

Google: "Keynote: Recent Advances in Artificial Intelligence via Machine Learning and the Implications for Computer System Design"

Jeff Dean这次的Keynote已经被转载介绍了很多了,我就不重复了。贴两张我比较关注的Slides。

这是第一次看到TPUv2的框图,虽然信息很少,应该也可以算是一个重要事件了。

T.S.:

从去年开始,AI相关的芯片越来越热。传统芯片公司都有所布局,很多软件和互联网公司纷纷进入,Startup们的估值越来越高。芯片是未来AI发展的基础,热度高是很自然的,但热度并不意味着成功,希望还在路上的各位最终都能成功。

Previous:西数娶东芝?暂时没戏!大客户苹果联手SK海力士抢亲

Online messageinquiry

央视报道:国产AI芯片重大突破!

马来西亚,首款自研AI芯片发布

一文了解AI芯片的常见应用领域

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| TL431ACLPR | Texas Instruments | |

| CDZVT2R20B | ROHM Semiconductor | |

| MC33074DR2G | onsemi | |

| RB751G-40T2R | ROHM Semiconductor | |

| BD71847AMWV-E2 | ROHM Semiconductor |

| model | brand | To snap up |

|---|---|---|

| BP3621 | ROHM Semiconductor | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: